#### VLSI Signal Processing

Lecture 9 Redundant Arithmetic

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

9-1

A

#### Redundant?

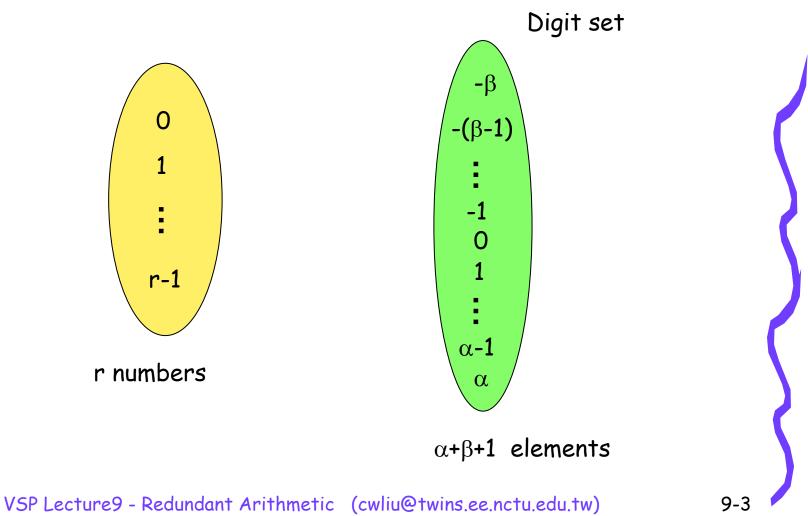

- A non-redundant radix-r number has digits from the set {0,1,...,r-1} and all numbers can be represented in a unique way

- A radix-r redundant signed-digit number system is based on digit set  $S = \{-\beta, ..., -1, 0, 1, ..., \alpha\}$ , where  $1 \le \beta, \alpha \le r-1$

- The digit set S contains more than r values

→ multiple

representations for any number in signed digit format.

Hence, the name redundant

- A symmetric signed digit has  $\alpha = \beta$ .

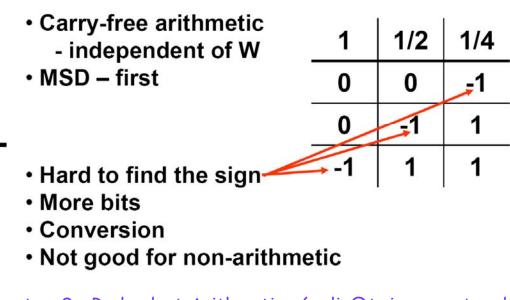

- Carry-free addition is one of the most attractive properties of redundant signed-digit numbers. This allows most significant digit (MSD) first redundant arithmetic, also called on-line arithmetic (division..)

1-1 onto Mapping?

#### Redundant Number Representations

- A symmetric signed-digit representation uses the digit set  $D_{r,\alpha} = \{-\alpha, ..., -1, 0, 1, ..., \alpha\}$ , where r is the radix and  $\alpha$  the largest digit in the set.

- A number in this representation is written as:

$$X_{r,\alpha} = X_{W-1} \cdot X_{W-2} \dots X_1 X_0 = \sum X_{W-1-i} r^i$$

- The sign of the number X is given by the sign of the most significant non-zero digit

- If  $2\alpha$ +1<r, the digit set  $D_{(r,\alpha)}$  is incomplete (i.e. some numbers cannot be represented)

- If  $2\alpha$ +1=r, the digit set  $D_{\langle r,\alpha \rangle}$  is complete but not redundant

- If  $2\alpha$ +1>r, the digit set  $D_{(r,\alpha)}$  is redundant

#### Example

• Signed-Digit Numbers  $X_{(r,\alpha)} = x_{W-1} \cdot x_{W-2} \dots x_1 x_0 = \sum x_{W-1-i} r^i$

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

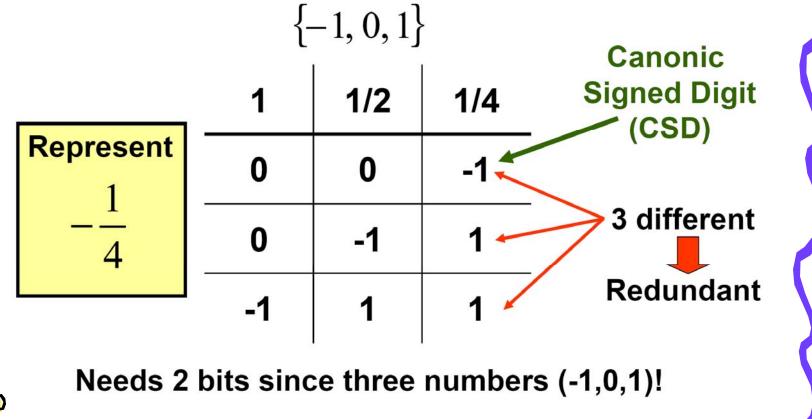

#### Review of Canonical Signed Digit

- Minimum number of non-zero bits

- A sequence of ones can be replaced with

- A "-1" at the least significant position of the sequence

- A "1" at the position to the left of the most significant position of the sequence

- Zeros between the "1" and the "-1"

- Save more than 2/3 of the adder cells at an average

- Redundant factor

- A measure of the redundancy of a symmetric signed-digit representations :  $\rho = \alpha/(r-1)$

| Digit Set D <sub><r.α></r.α></sub> | α           | Redundancy Factor $\rho$ |

|------------------------------------|-------------|--------------------------|

| Incomplete                         | < (r - 1)/2 | $<\frac{1}{2}$           |

| Complete but non-redundant         | = (r - 1)/2 | $=\frac{1}{2}$           |

| Redundant                          | ≥[r/2]      | > 1/2                    |

| Minimally redundant                | =[r/2]      | > 1/2 and < 1            |

| Maximally redundant                | = r - 1     | = 1                      |

| Over-redundant                     | >r-1        | > 1                      |

#### Redundancy Characteristic Example

Radix 4 with digit set {-2,-1,0,1,2}  $\rho = \frac{\alpha}{r-1} = \frac{2}{3} \quad \longrightarrow \text{ Minimally redundant}$

Radix 4 with digit set {-3,-2,-1,0,1,2,3}  $\rho = \frac{\alpha}{r-1} = \frac{3}{3} \implies \text{Maximally redundant}$

Carry-Free?

- Redundant number representations limit the carry propagation to a few bit-positions, which is usually independent of the wordlength W.

- + and -

- +

### **Redundant** Arithmetic

•

$$X_{} = X^+ - X^-, Y_{} = Y^+ - Y^-$$

- Hybrid radix-r addition  $X_{r,\alpha}$  + Y

- Hybrid radix-r subtraction  $X_{r,\alpha}$  Y

- A signed-digit addition/subtraction can then be viewed as a concatenation of one hybrid addition/subtraction and one hybrid subtraction/addition

# Hybrid Radix-2 Addition

Signed digit number  $\{-1, 0, 1\}$

S<sub><2.1></sub> = X<sub><2.1></sub> + Y ← unsigned

where,  $X_{x_{r,\alpha}} = x_{W-1} \cdot x_{W-2} x_{W-3} \cdot x_0$ ,  $Y = y_{W-1} \cdot y_{W-2} y_{W-3} \cdot y_0$ . The addition is carried out in two steps :

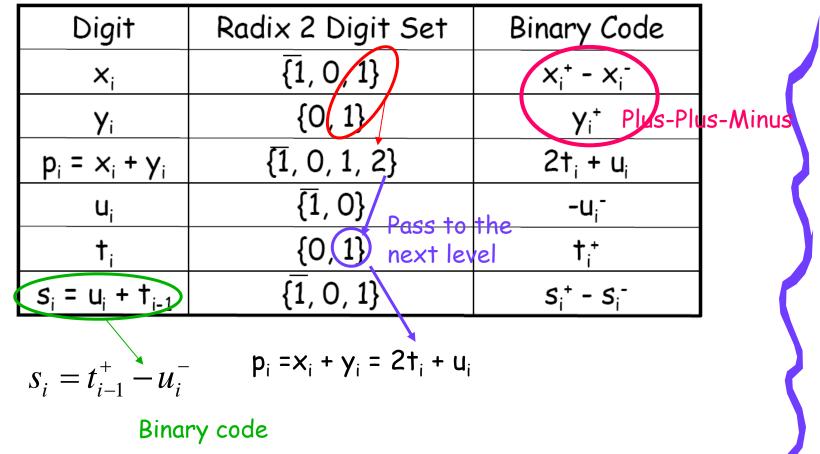

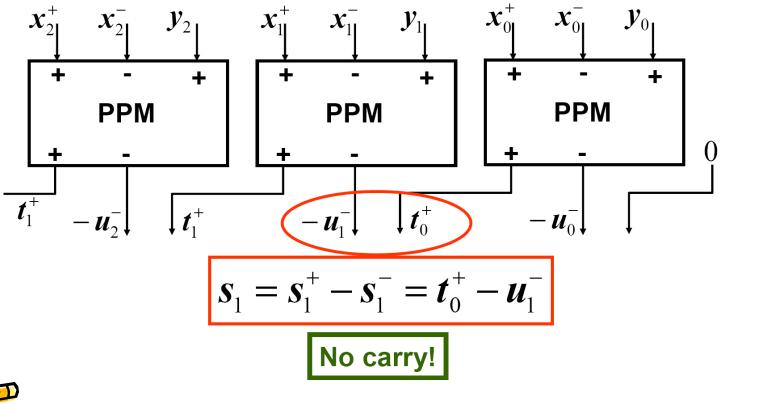

1. The 1<sup>st</sup> step is carried out in parallel for all the bit positions. An intermediate sum  $p_i = x_i + y_i$  is computed, which lies in the range  $\{\overline{1}, 0, 1, 2\}$ . The addition is expressed as:

$$x_i + y_i = 2t_i + u_i$$

where  $t_i$  is the transfer digit and has value 0 or 1, and is denoted as  $t_i^+$ ;  $u_i$  is the interim sum and has value either 1 or 0 and is denoted as  $-u_i^-$ .  $t_{-1}$  is assigned the value of 0.

2. The sum digits  $s_i$  are formed as follows:

# Hybrid Radix-2 Addition

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

# Hybrid Radix-2 Adder

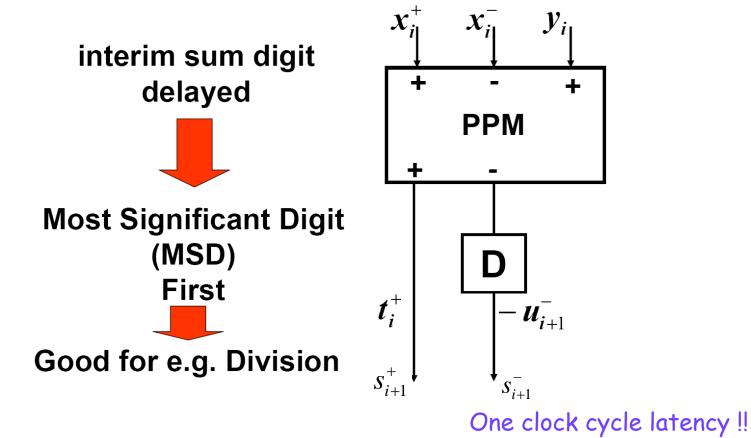

PPM: Plus-Plus-Minus adder (Full adder)

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

# Example

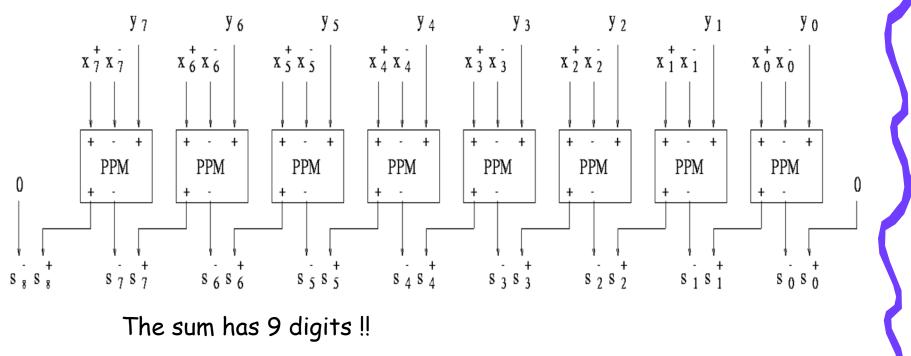

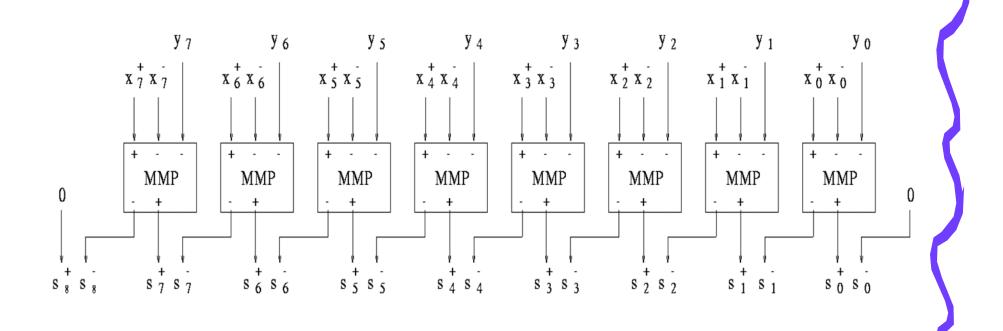

Eight-digit hybrid radix-2 adder

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

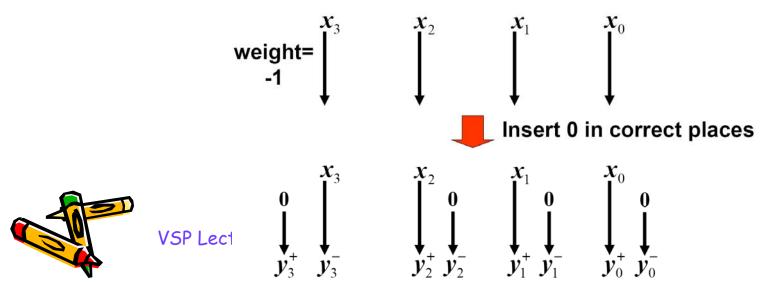

Note: a zero digit needs to be inserted between 2 consecutive input operands VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

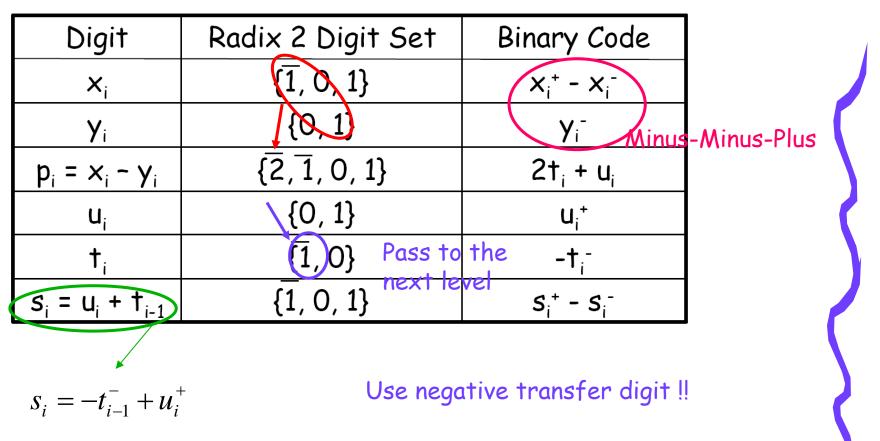

# Hybrid Radix-2 Subtraction

Signed digit number  $\{-1, 0, 1\}$

S<sub><2.1></sub> = X<sub><2.1></sub> − Y ← unsigned

where,  $X_{(r,\alpha)} = x_{W-1} \cdot x_{W-2} x_{W-3} \cdot x_0$ ,  $Y = y_{W-1} \cdot y_{W-2} y_{W-3} \cdot y_0$ . The subtraction is carried out in two steps :

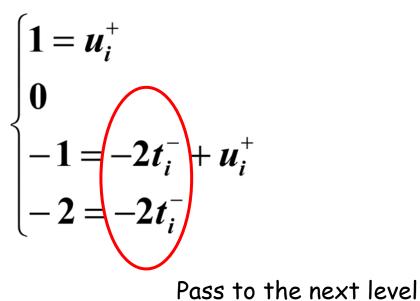

The 1<sup>s+</sup> step is carried out in parallel for all the bit positions. An intermediate difference p<sub>i</sub> = x<sub>i</sub> - y<sub>i</sub> is computed, which lies in the range {2, 1, 0, 1}. The addition is expressed as:

$$x_i - y_i = 2t_i + u_i$$

where  $t_i$  is the transfer digit and has value 1 or 0, and is denoted as  $-t_i^-$ ;  $u_i$  is the interim sum and has value either 0 or 1 and is denoted as  $u_i^+$ .  $t_{-1}$  is assigned the value of 0.

2. The sum digits  $s_i$  are formed as follows:

# Hybrid Radix-2 Subtraction

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

#### Remarks

•  $\{-1, 0, 1\}$  -  $\{0, 1\} = \{-2, -1, 0, 1\}$

$$x_i = x_i^+ - x_i^- \qquad \qquad y_i$$

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

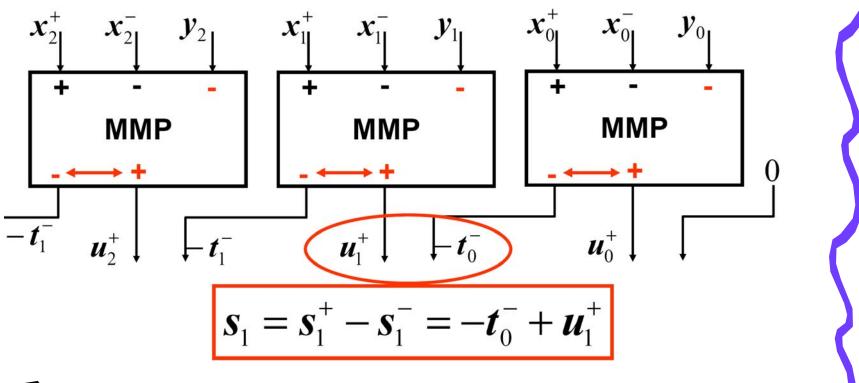

# Hybrid Radix-2 Subtractor

• MMP: Minus-Minus-Plus adder (Full adder)

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

# Example

Eight-digit hybrid radix-2 subtractor

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

9-22

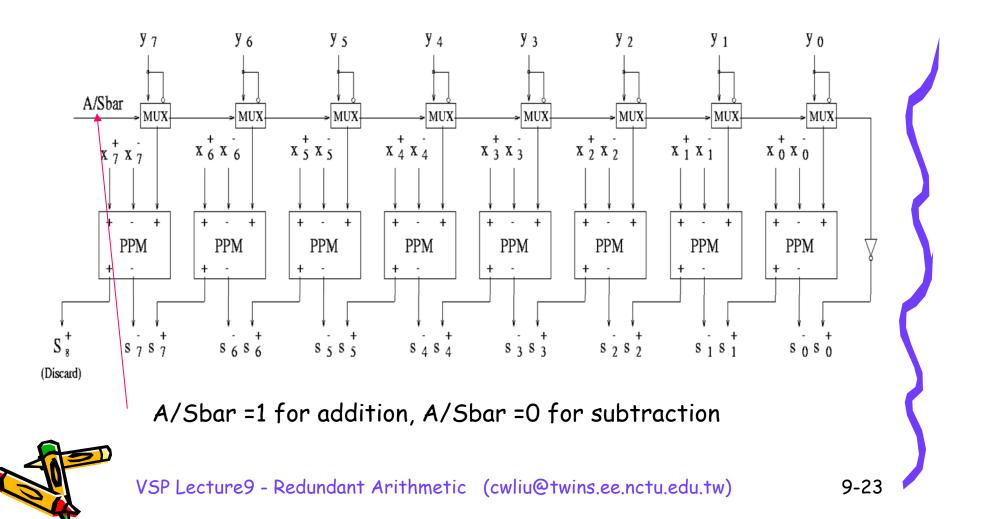

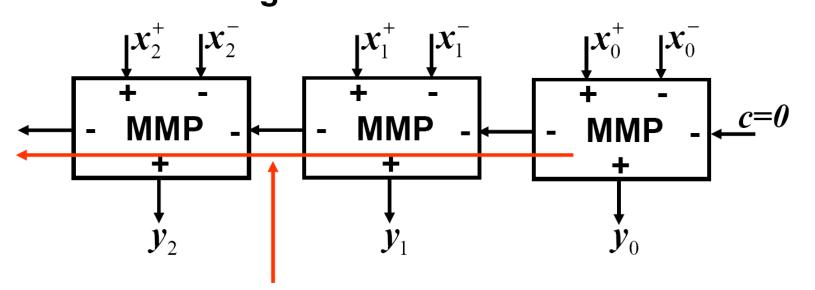

#### Hybrid Radix-2 Addition/Subtraction

### Signed-Binary Digit (SBD) Arithmetic

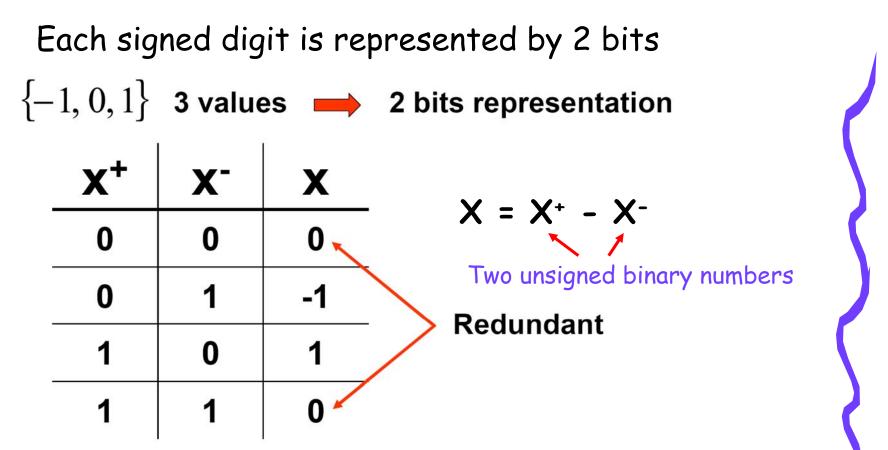

- $Y_{r,\alpha}$  = Y<sup>+</sup> Y<sup>-</sup>, is a signed digit number, where Y<sup>+</sup> and Y<sup>-</sup> are from the digit set {0, 1, ...,  $\alpha$ }.

- A signed digit number is thus subtraction of 2 unsigned conventional numbers.

- Signed addition is given by:

$$S_{(r,\alpha)} = X_{(r,\alpha)} + Y_{(r,\alpha)} = X_{(r,\alpha)} + Y^{+} - Y^{-},$$

$$\Rightarrow S1_{(r,\alpha)} = X_{(r,\alpha)} + Y^{+},$$

$$S_{(r,\alpha)} = S1_{(r,\alpha)} - Y^{-}$$

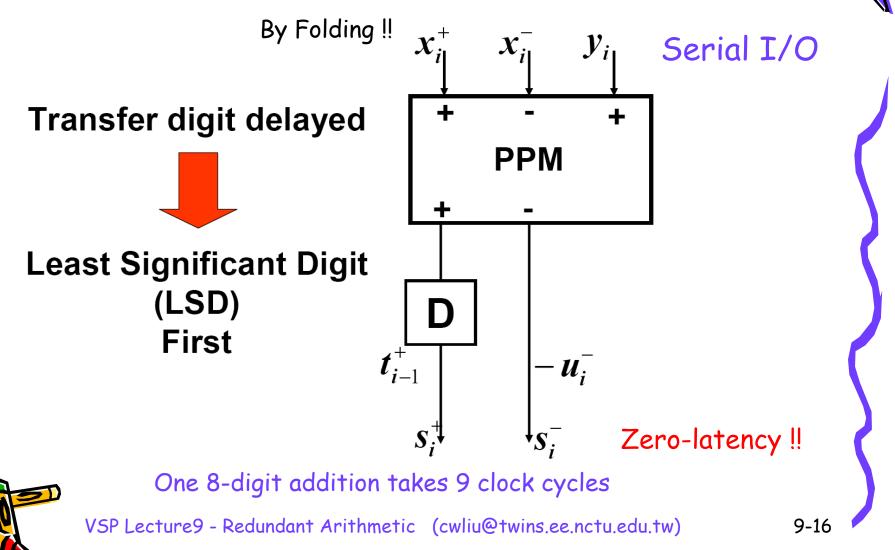

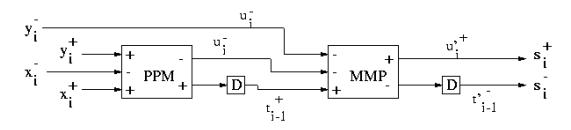

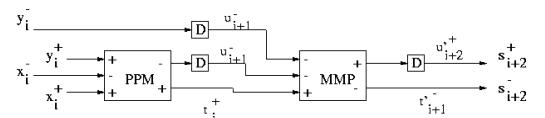

Digit serial SBD adders can be derived by folding the digit parallel adders in both lsd-first and msdfirst modes.

LSD-first adders have zero latency and msd-first adders have latency of 2 clock cycles.

### Signed Binary Digit Arithmetic

- $Y_{r,\alpha}$  = Y<sup>+</sup> -Y<sup>-</sup>, is a signed digit number, where Y<sup>+</sup> and Y<sup>-</sup> are (unsigned conventional numbers) from the digit set {0,1,..., $\alpha$ }.

- Signed addition is given by

у <del>6</del> У 6 y 5 y 5 y 4 y 4 y 3 y 3 y <sup>+</sup><sub>2</sub> y <sup>-</sup><sub>2</sub> y 1 y 1 y 7 y 7 Уо́Уо  $A/\overline{S}$  $x_{7}^{+}x_{7}^{-}$ x 6 x 6  $x_{5}^{+}x_{5}^{-}$  $x_{4}^{+}x_{4}^{-}$ x 3 x 3  $x_{2}^{+}x_{2}^{-}$  $x_{1}^{+}x_{1}^{-}$  $x_{0}^{+}x_{0}^{-}$ + - + PPM PPM PPM PPM PPM PPM PPM PPM 0 S .\* MMP MMP MMP MMP MMP MMP MMP MMP s 7 s 7 \$ 6 \$ 6 8 5 8 5  $s_{4}^{+}s_{4}^{-}$ s 3 S 3  $s_{2}^{+} s_{2}^{-}$ s 1 s 1 s 0 s 0 S, VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

9-25

$S_{<\mathbf{r},\alpha>}=X_{<\mathbf{r},\alpha>}+Y_{<\mathbf{r},\alpha>}=(X_{<\mathbf{r},\alpha>}+Y^{+})-Y^{-}$

#### Remarks

- Signed-digit addition can be viewed as a concatenation of one hybrid addition and one hybrid subtraction.

- Digit-serial redundant adders can be derived by folding methodology (LSD-first, or MSD-first)

- LSD-first adders have zero latency, while MSD-first adders have 2 clock cycles latency.

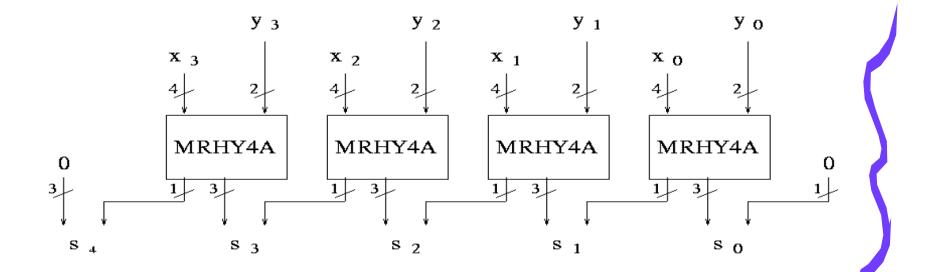

# Hybrid Radix-4 Addition

- Higher order radices can be employed to reduce the number of iteration cycles.

- Maximally redundant hybrid radix-4 addition (MRHY4A) considers the numbers based on digit set  $D_{4,3}$ ={-3,-2,-1,0,1,2,3},  $\rho$ =1

- Minimally redundant hybrid radix-4 addition (mrHY4A) considers the numbers based on digit set D<sub><4,2></sub>={-2,-1,0,1,2}, o=2/3

#### MRHY4A

$$S_{(4.3)} = X_{(4.3)} - Y_4 \leftarrow unsigned$$

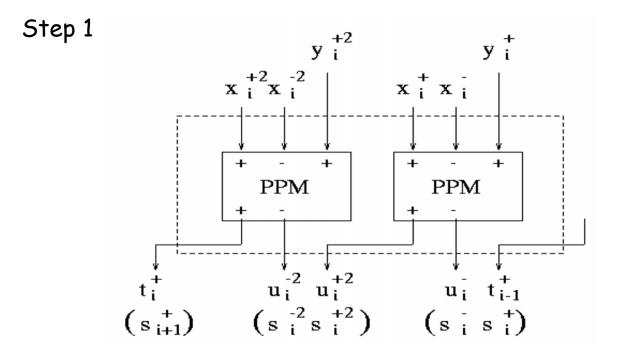

• The first step computes:

$$x_{i} + y_{i} = 4t_{i} + u_{i}$$

Replacing the respective binary codes from the table the following is obtained :

$(2x_i^{+2} - 2x_i^{-2} + 2y_i^{+2}) + x_i^+ - x_i^- + y_i^+ = 4t_i^+ + 2u_i^{+2} - 2u_i^{-2} - u_i^-$ A MRHY4A cell consisting of two PPM adders is used to compute the above.

• Step 2 computes computes  $s_i = t_{i-1} + u_i$ . Replacing  $s_i$ ,  $u_i$ , and  $t_{i-1}$  by corresponding binary codes leads to  $s_i^{+2} = u_i^{+2}$ ,  $s_i^{-2} = u_i^{-2}$ ,  $s_i^{+}=t_{i-1}^{+}$  and  $s_i^{-} = u_i^{-2}$ .

#### **Digit Sets in MRHR4A** D<sub>(4,3)</sub>={-3,-2,-1,0,1,2,3},

Digit Radix 4 Digit Set Binary Code  $\{\overline{3}, \overline{2}, \overline{1}, 0, 1, 2, 3\}$ PPM  $2x_i^{+2} - 2x_i^{-2} + x_i^{+} - x_i^{-1}$ Xi 2y<sub>i</sub><sup>+2</sup> + y<sub>i</sub><sup>+</sup>  $\{0, 1, 2, 3\}$ Yi  $\{\overline{3}, \overline{2}, \overline{1}, 0, 1, 2, \overline{3}, 4, 5, 6\}$  $4t_{i} + u_{i}$  $\mathbf{p}_i = \mathbf{x}_i + \mathbf{y}_i$  $2u_{i}^{+2} - 2u_{i}^{-2} - u_{i}^{-2}$  $\{\overline{3}, \overline{2}, \overline{1}, 0, 1, 2\}$ **U**<sub>i</sub> Pass to the {O(1) next level  $\{\overline{3}, \overline{2}, \overline{1}, 0, 1, 2, 3\}$  $2s_i^{+2} - 2s_i^{-2} + s_i^{+} - s_i^{-}$  $s_{i} = u_{i} + t_{i-1}$

$$x_i + y_i = p_i = 4t_i + u_i$$

$s_i = u_i + t_{i-1}$ , where  $s_i^{+2} = u_i^{+2}$ ,  $s_i^{-2} = u_i^{-2}$ ,  $s_i^+ = t_{i-1}^+$ ,  $s_i^- = u_i^-$

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

#### MRHY4A Adder Cell

2PPM (full) adders that perform the 2 grouped additions in parallel and reduce the number of bits from 6 to 4 with the weights.

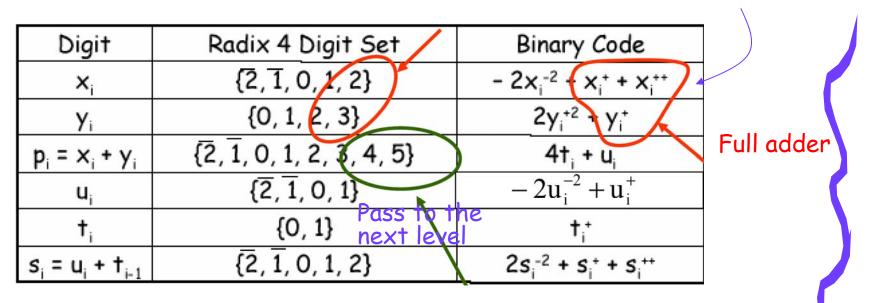

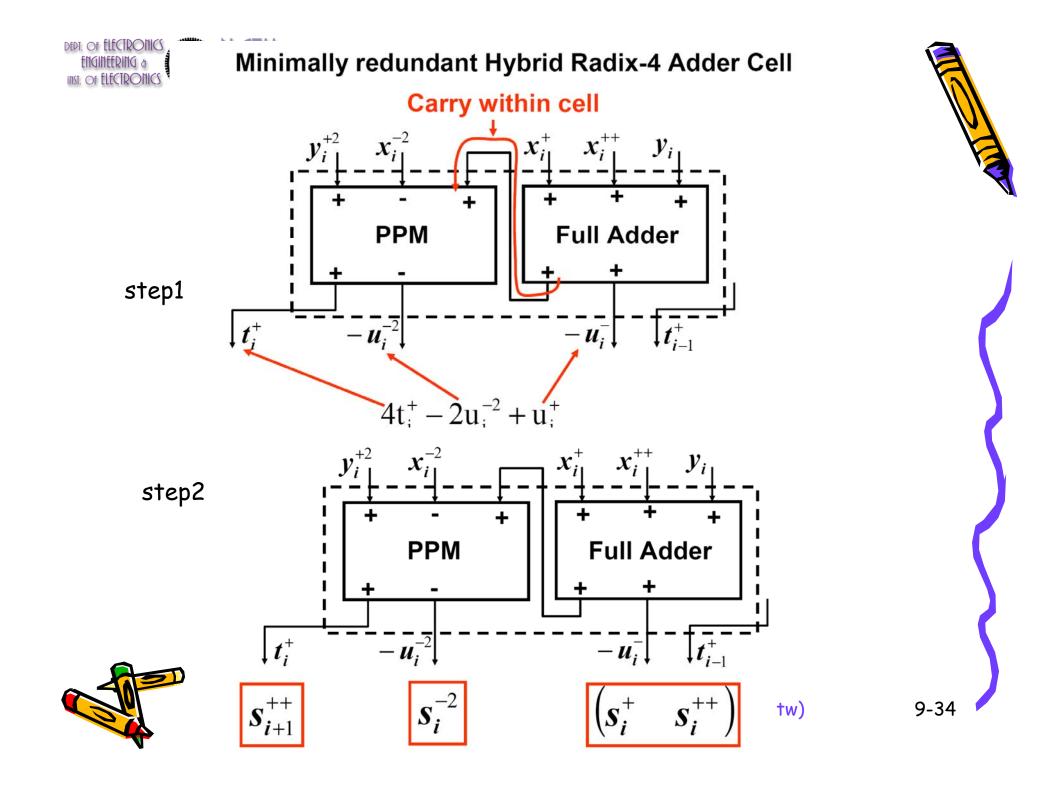

#### mrHY4A

$$S_{(4,2)} = X_{(4,2)} + Y_4 - unsigned$$

• The first step computes:

$$x_{i} + y_{i} = 4t_{i} + u_{i}$$

Replacing the respective binary codes from the table the following is obtained :

$(-2x_i^{-2} + 2y_i^{+2}) + (x_i^{+} + x_i^{++} + y_i^{+}) = 4t_i^{+} - 2u_i^{-2} + u_i^{+}$ A mrHY4A cell consisting of one PPM adder and a full adder is used to compute the above.

Step 2 computes computes  $s_i = t_{i-1} + u_i$ . Replacing  $s_i$ ,  $u_i$ , and  $t_{i-1}$  by corresponding binary codes leads to  $s_i^{-2} = u_i^{-2}$ ,  $s_i^{++} = t_{i-1}^{++}$  and  $s_i^{+} = u_i^{+}$ .

# Digit Sets in mrHY4A

D<sub><4,2></sub>={-2,-1,0,1,2} The digit number is represented by 3 bits!!

$$x_i + y_i = p_i = 4t_i + u_i$$

$$s_i = u_i + t_{i-1}$$

#### Non-Redundant to Redundant Conversion

- The non-redundant input digit set can be considered as a subset of the redundant input digit set.

- Radix-2 representation:

- A non-redundant number  $X = x_3 \circ x_2 x_1 x_0$  can be converted to a redundant number  $Y = y_3 \circ y_2 y_1 y_0$ , where each digit  $y_i$  is encoded as  $y_i^+$  and  $y_i^-$  as shown below

#### Non-Redundant to Redundant Conversion

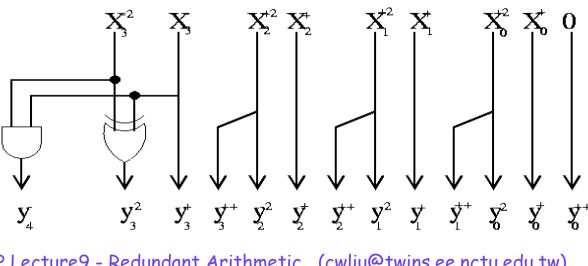

- Radix-4 representation

- X is a radix-4 complement number, whose digits  $x_i$ 's are encoded using 2 wires as  $x_i = 2x_i^{+2} + x_i^+$ . Its corresponding maximally redundant number Y is encoded using  $y_i=2y_i^{+2}-2y_i^{-2}+y_i^+-y_i^-$ . The sign digit  $x_3$  can take values -3, -2, -1, or 0, and is encoded using  $x_3=-2x_3^{-2}-x_3^-$ .

radix-4 minimally redundant number: X is a radix-4 complement number, whose digits  $x_i$  are encoded using 2 wires as  $x_i = 2x_i^{+2} + x_i^{+}$ . Its corresponding minimally redundant number Y is encoded using  $y_i = -2y_i^{-2} + y_i^{+} + y_i^{++}$ . To convert radix-r number x to redundant number  $y_{ra}$ , the digits in the range [ $\alpha$ , r - 1] are encoded using a transfer digit 1 and a corresponding digit  $x_i - r$  where  $x_i$ is the  $i^{th}$  digit of x. Thus,

$$2x_{i}^{+2} + x_{i}^{+} = 4x_{i}^{+2} - 2x_{i}^{+2} + x_{i}^{+}$$

$$= y_{i+1}^{++} - 2y_{i}^{-2} + y_{i}^{+}$$

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)

- In general, it is not possible to know the value of any of nonredundant digits until the least significant redundant digit become available

- Example

- 10001 → (03333)<sub>4</sub>

- 10001 → (10001)<sub>4</sub>

To change the least significant digit from -1 to 1 causes all of the preceding (more significant) digits to be changed

#### **Redundant to Non-red Conversion**

#### In general not possible to output ANY digit until LSD has been processed, i.e. advatage of MSD first "removed"

#### **Introduces Carry-ripple**

If a redundant number is scanned msd-first and transformed to a nonredundant radix-4 format

VSP Lecture9 - Redundant Arithmetic (cwliu@twins.ee.nctu.edu.tw)