# Chapter 2

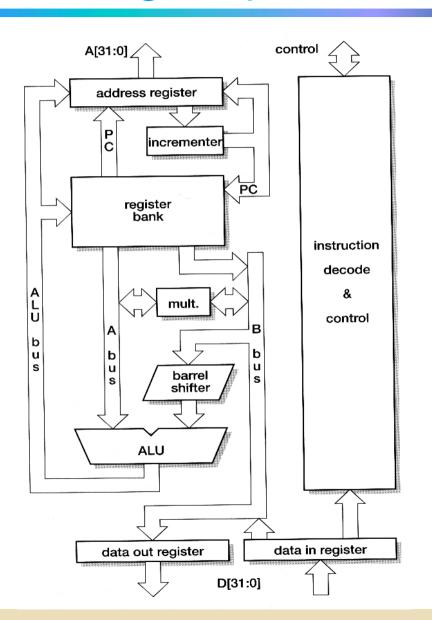

### **ARM Processor Core and Instruction Sets**

C. W. Jen 任建葳

cwjen@twins.ee.nctu.edu.tw

### **Outline**

- Processor programming model

- 32-bit instruction set

- 16-bit instruction set

- ARM processor core

- Software development

## Processor Programming Model

### **ARM Ltd**

- ARM was originally developed at Acron Computer Limited of Cambridge, England between 1983 and 1985

- 1980, RISC concept at Stanford and Berkeley universities

- first RISC processor for commercial use

- 1990 Nov, ARM Ltd was founded

- ARM cores

licensed to partners who fabricate and sell to customers

- Technologies assist to design in the ARM application

- Software tools, boards, debug hardware, application software, bus architectures, peripherals etc...

## ARM Architecture vs. Berkeley RISC

#### Features used

- load/store architecture

- fixed-length 32-bit instructions

- 3-address instruction formats

#### Features unused

- register windows ⇒ costly

use shadow registers in ARM

- delayed branch ⇒ not well to superscalar

badly with branch prediction

- single-cycle execution of all instructions most single-cycle

- memory access

multiple cycles when no separate data and instruction memory support

auto-indexing addressing modes

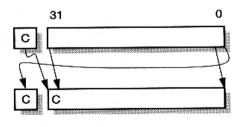

### Data Size and Instruction set

- ARM processor is a 32-bit architecture

- Most ARM's implement two instruction sets

- 32-bit ARM instruction set

- 16-bit Thumb instruction set

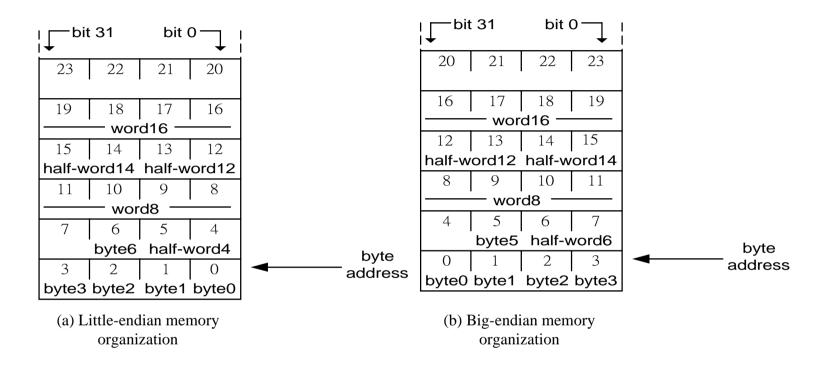

## Data Types

- ARM processor supports 6 data types

- 8-bits signed and unsigned bytes

- 16-bits signed and unsigned half-words, aligned on 2-byte boundaries

- 32-bits signed and unsigned words, aligned on 4-byte boundaries

- ARM instructions are all 32-bit words, word-aligned Thumb instructions are half-words, aligned on 2-byte boundaries

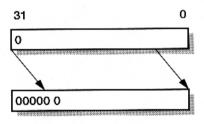

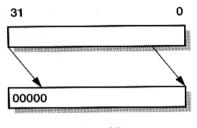

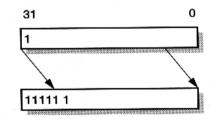

- Internally all ARM operations are on 32-bit operands; the shorter data types are only supported by data transfer instructions. When a byte is loaded form memory, it is zeroor sign-extended to 32 bits

- ARM coprocessor supports floating-point values

# **Programming Model**

Each instruction can be viewed as performing a defined transformation of the states

visible registers

invisible registers

system memory

user memory

### **Processor Modes**

- ARM has seven basic operating modes

- Mode changes by software control or external interrupts

| CPRS[4:0] | Mode   | Use                                   | Registers |

|-----------|--------|---------------------------------------|-----------|

| 10000     | User   | Normal user code                      | User      |

| 10001     | FIQ    | Processing fast interruptsfiq         |           |

| 10010     | IRQ    | Processing standard interrupts        | _irp      |

| 10011     | SVC    | Processing software interrupts (SWIs) | _svc      |

| 10111     | Abort  | Processing memory faultsabt           |           |

| 11011     | Undef  | Handling undefined instruction traps  | _und      |

| 11111     | System | Running privileged operating system   | user      |

# Privileged Modes

- Most programs operate in user mode. ARM has other privileges operating modes which are used to handle exceptions, supervisor calls (software interrupts), and system mode

- More access rights to memory systems and coprocessors

- Current operating mode is defined by CPSR[4:0]

## Supervisor Mode

- Having some protective privileges

- System-level function (transaction with the outside world) can be accessed through specified supervisor calls

- Usually implemented by software interrupt (SWI)

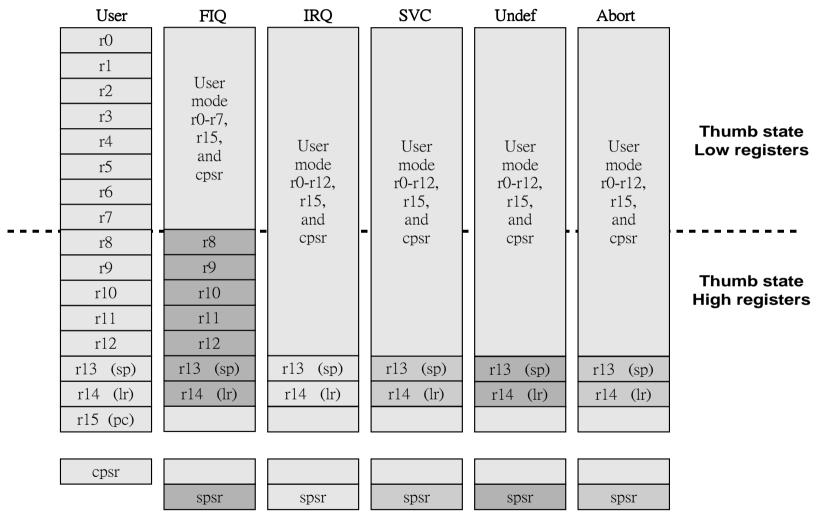

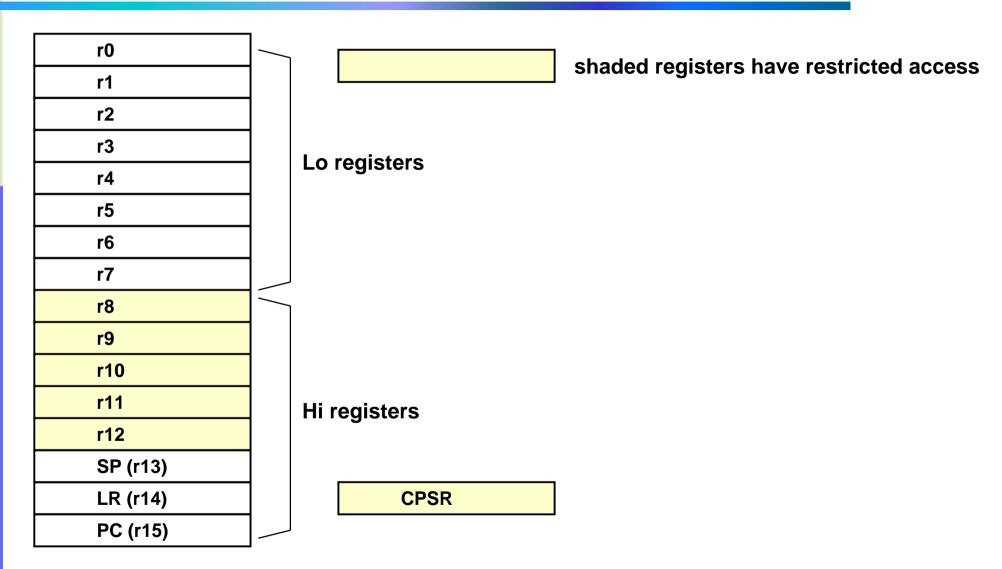

## The Registers

- ARM has 37 registers, all of which are 32 bits long

- 1 dedicated program counter

- 1 dedicated current program status register

- 5 dedicated saved program status registers

- 30 general purpose registers

- The current processor mode governs which bank is accessible

- each mode can access

- a particular set of r0-r12 registers

- a particular r13 (stack pointer, SP) and r14 (link register, LR)

- the program counter, r15 (PC)

- the current program status register, CPSR

- privileged modes (except System) can access

- a particular SPSR (saved program status register)

# Register Banking

#### Current Visible Registers

User Mode

| r0       |  |  |  |  |

|----------|--|--|--|--|

| r1       |  |  |  |  |

| r2       |  |  |  |  |

| r3       |  |  |  |  |

| r4       |  |  |  |  |

| r5       |  |  |  |  |

| r6       |  |  |  |  |

| r7       |  |  |  |  |

| r8       |  |  |  |  |

| r9       |  |  |  |  |

| r10      |  |  |  |  |

| r11      |  |  |  |  |

| r12      |  |  |  |  |

| r13 (sp) |  |  |  |  |

| r14 (lr) |  |  |  |  |

| r15 (pc) |  |  |  |  |

cpsr

#### Banked out Registers

| FIQ                         | IRQ                  | SVC                  | Undef                | Abort                |

|-----------------------------|----------------------|----------------------|----------------------|----------------------|

| r8<br>r9<br>r10<br>r11      |                      |                      |                      |                      |

| r12<br>r13 (sp)<br>r14 (lr) | r13 (sp)<br>r14 (lr) | r13 (sp)<br>r14 (lr) | r13 (sp)<br>r14 (lr) | r13 (sp)<br>r14 (lr) |

| spsr                        | spsr                 | spsr                 | spsr                 | spsr                 |

# Registers Organization Summary

Note: System mode uses the User mode reigster set

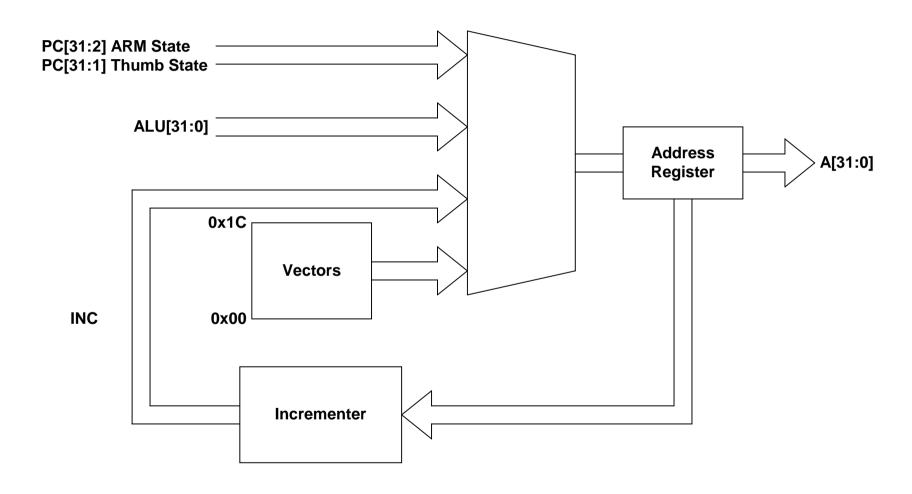

# Program Counter (r15)

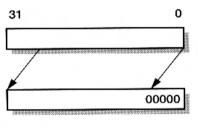

- When the processor is executing in ARM state:

- all instructions are 32 bits wide

- all instructions must be word-aligned

- therefore the PC value is stored in bits [31:2] with bits

[1:0] undefined (as instruction cannot be halfword or byte aligned)

- When the processor is executing in Thumb state:

- all instructions are 16 bits wide

- all instructions are must be halfword-aligned

- therefore the PC value is stored in bits [31:1] with bit [0] undefined (as instruction cannot be byte-aligned)

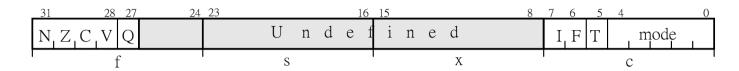

# Program Status Registers (CPSR)

- Condition code flags

- N: Negative result from ALU

- Z : Zero result from ALU

- C: ALU operation Carried out

- V : ALU operation oVerflowed

- Sticky overflow flag Q flag

- architecture 5TE only

- indicates if saturation has occurred during certain operations

- Interrupt disable bits

- I = 1, disables the IRQ

- F = 1, disables the FIQ

- T Bit

- architecture xT only

- T = 0, processor in ARM state

- T = 1, processor in Thumb state

- Mode bits

- specify the processor mode

### **SPSRs**

- Each privileged mode (except system mode) has associated with it a Save Program Status Register, or SPSR

- This SPSR is used to save the state of CPSR (Current Program Status Register) when the privileged mode is entered in order that the user state can be fully restored when the user process is resumed

- Often the SPSR may be untouched from the time the privileged mode is entered to the time it is used to restore the CPSR, but if the privileged supervisor calls to itself) then the SPSR must be copied into a general register and saved

## Exceptions

- Exceptions are usually used to handle unexpected events which arise during the execution of a program, such as interrupts or memory faults, also cover software interrupts, undefined instruction traps, and the system reset

- Three groups :

- generated as the direct effect of executing an instruction software interrupts, undefined instructions, prefetch abort (memory fault)

- generated as the side-effect of an instruction data aborts

- generated externally reset, IRQ, FIQ

# Exception Entry (1/2)

- When an exception arises, ARM completes the current instruction as best it can (except that reset exception terminates the current instruction immediately) and then departs from the current instruction sequence to handle the exception which starts from a specific location (exception vector)

- Processor performs the following sequence

- change to the operating mode corresponding to the particular exception

- save the address of the instruction following the exception entry instruction in r14 of the new mode

- save the old value of CPSR in the SPSR of the new mode

- disable IRQs by setting bit of the CPSR, and if the exception is a fast interrupt, disable further faster interrupt by setting bit of the CPSR

# Exception Entry (2/2)

force the PC to begin executing at the relevant vector address

| Exception                                       | Mode  | Vector address |

|-------------------------------------------------|-------|----------------|

| Reset                                           | SVC   | 0x00000000     |

| Undefined instruction                           | UND   | 0x00000004     |

| Software interrupt (SWI)                        | SVC   | 0x00000008     |

| Prefetch abort (instruction fetch memory fault) | Abort | 0x000000C      |

| Data abort (data access memory fault)           | Abort | 0x0000010      |

| IRQ (normal interrupt)                          | IRQ   | 0x00000018     |

| FIQ (fast interrupt)                            | FIQ   | 0x000001C      |

- Normally the vector address contains a branch to the relevant routine, though the FIQ code can start immediately

- Two banked registers in each of the privilege modes are used to hold the return address and stack pointer

# Exception Return (1/3)

- Once the exception has been handled, the user task is normally resumed

- The sequence is

- any modified user registers must be restored from the handler'stack

- CPSR must be restored from the appropriate SPSR

- PC must be changed back to the relevant instruction address

- The last two steps happen atomically as part of a single instruction

# Exception Return (2/3)

- When the return address has been kept in the banked r14

- to return from a SWI or undefined instruction trap MOVS PC, r14

- to return from an IRQ, FIQ or prefetch abort SUBS PC, r14, #4

- To return from a data abort to retry the data access

SUBS PC, r14, #8

- 'S' signifies when the destination register is the PC

# Exception Return (3/3)

When the return address has been saved onto a stack

```

LDMFD r13!,\{r0-r3,PC\}^{^{\prime}}; restore and return

```

- '^' indicates that this is a special form of the instruction the CPSR is restored at the same time that the PC is loaded from memory, which will always be the last item transferred from memory since the registers are loaded in increasing order

# **Exception Priorities**

- Priority order

- reset (highest priority)

- data abort

- FIQ

- IRQ

- prefetch abort

- SWI, undefined instruction

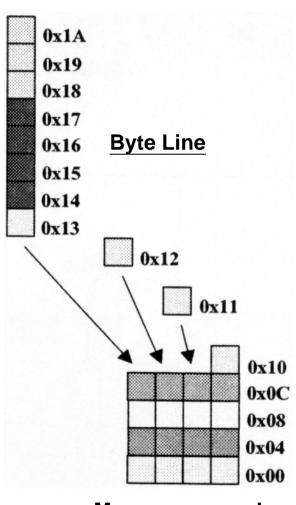

# **Memory Organization**

- Word, half-word alignment (xxxxoo or xxxxxo)

- ARM can be set up to access data in either littleendian or big-endian format

### Features of the ARM Instruction Set

- Load-store architecture

process values which are in registers

load, store instructions for memory data accesses

- 3-address data processing instructions

- Conditional execution of every instruction

- Load and store multiple registers

- Shift, ALU operation in a single instruction

- Open instruction set extension through the coprocessor instruction

- Very dense 16-bit compressed instruction set (Thumb)

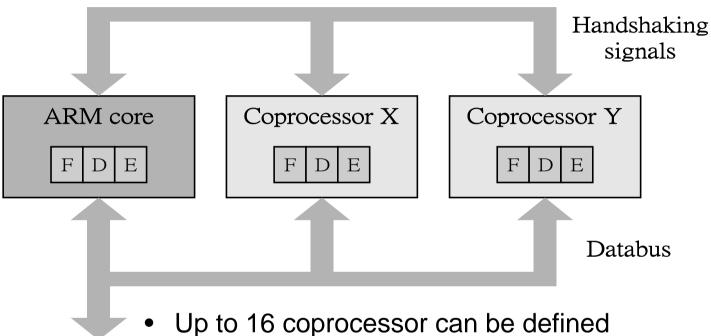

### Coprocessors

- Expands the ARM instruction set

- ARM uses them for "internal functions" so as not to enforce a particular memory map (eg cp15 is the ARM cache controller)

- Usually better for system designers to use memory mapped peripherals

- easier to implement

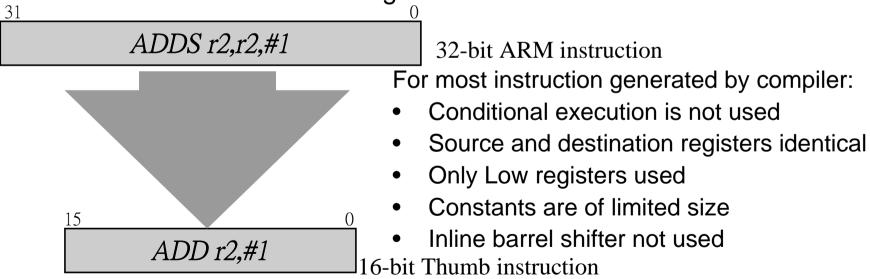

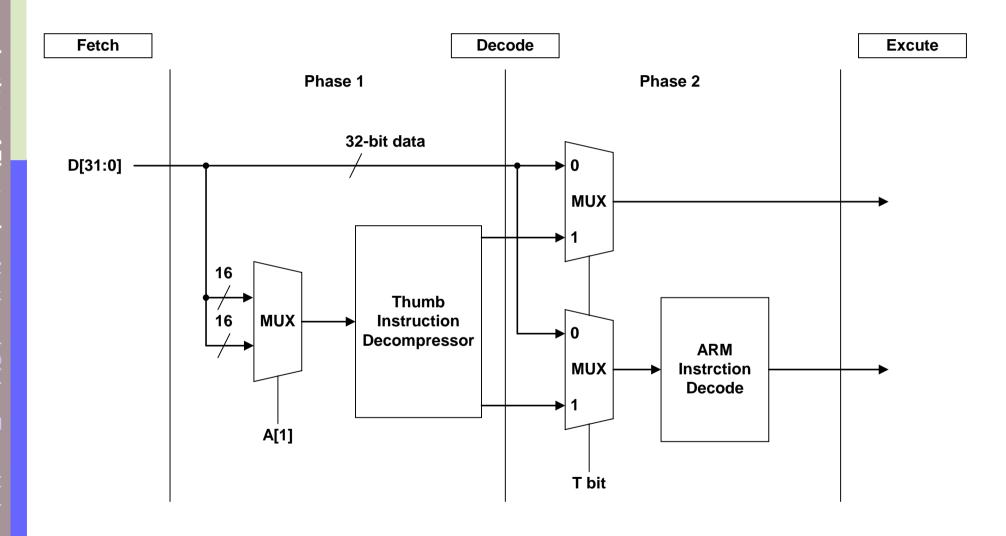

### **Thumb**

- Thumb is a 16-bit instruction set

- optimized for code density from C code

- improved performance from narrow memory

- subset of the fumctionality of the ARM instruction set

- Core has two execution states ARM and Thumb

- switch between them using BX instruction

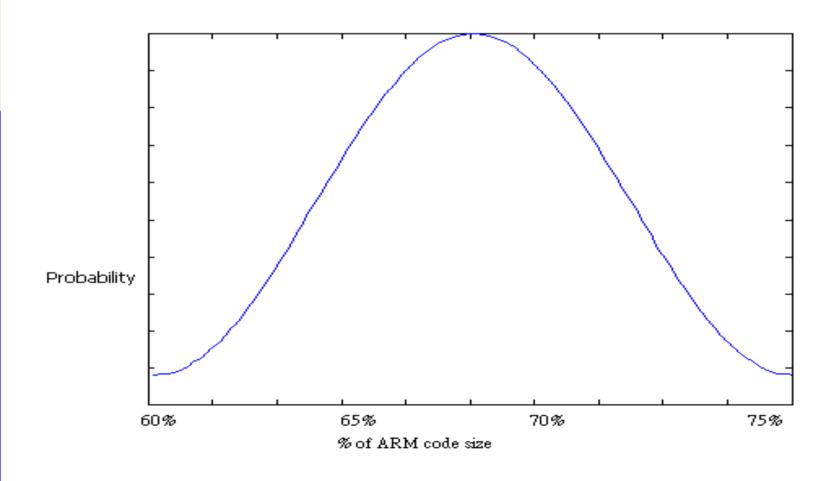

# Average Thumb Code Sizes

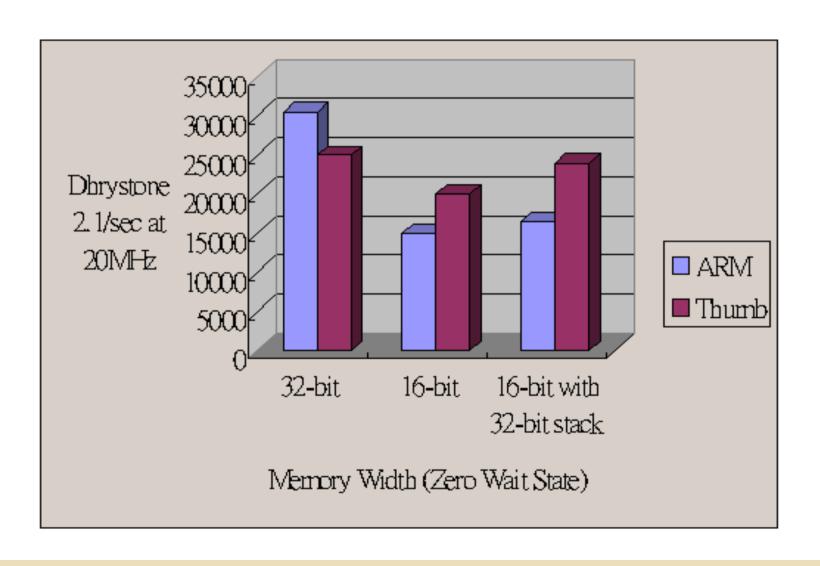

### **ARM** and Thumb Performace

# I/O System

- ARM handles input/output peripherals as memory-mapped with interrupt support

- Internal registers in I/O devices as addressable locations within ARM's memory map read and written using load-store instructions

- Interrupt by normal interrupt (IRQ)

or fast interrupt (FIQ)

higher priority

input signals are level-sensitive and maskable

- May include Direct Memory Access (DMA) hardware

# **ARM Exceptions**

- Supports interrupts, traps, supervisor calls

- When an exception occurs, the ARM:

- copies CPSR into SPSR\_<mode>

- sets appropriate CPSR bits

- if core currently in Thumb state then ARM state is entered

- mode field bits

- interrupt disable bits (if appropriate)

- stores the return address in LR\_<mode>

- set pc to vector address

- To return, exception handler needs to:

- restore CPSR from SPSR\_<mode>

- restore PC from LR\_<mode>

This can only be done in ARM state

| 0x1C | FIQ                   |  |  |

|------|-----------------------|--|--|

| 0x18 | IRQ                   |  |  |

| 0x14 | (Reserved)            |  |  |

| 0x10 | Data Abort            |  |  |

| 0x0C | Prefetch Abort        |  |  |

| 0x08 | Software Interrupt    |  |  |

| 0x04 | Undefined Instruction |  |  |

| 0x00 | Reset                 |  |  |

#### Vector Table

Vector table can be at 0xffff0000 on ARM720T and on ARM9/10 family devices

## **ARM Exceptions**

Exception handler use r13\_<mode> which will normally have been initialized to point to a dedicated stack in memory, to save some user registers for use as work registers

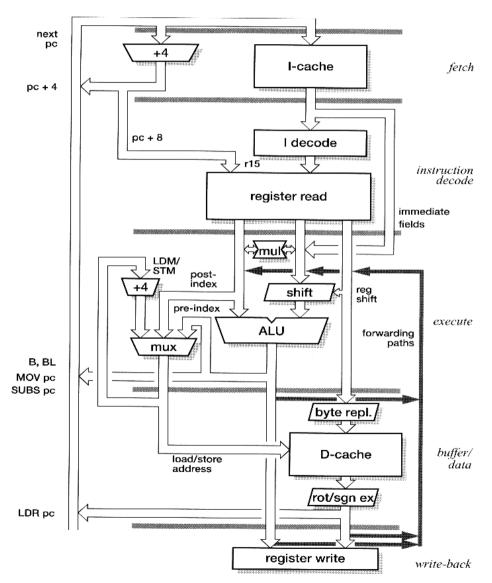

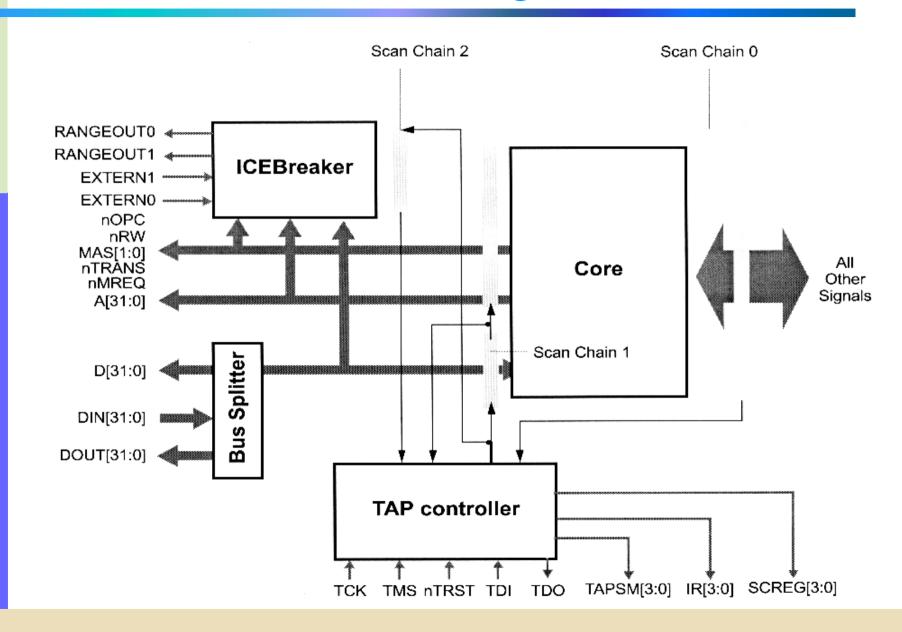

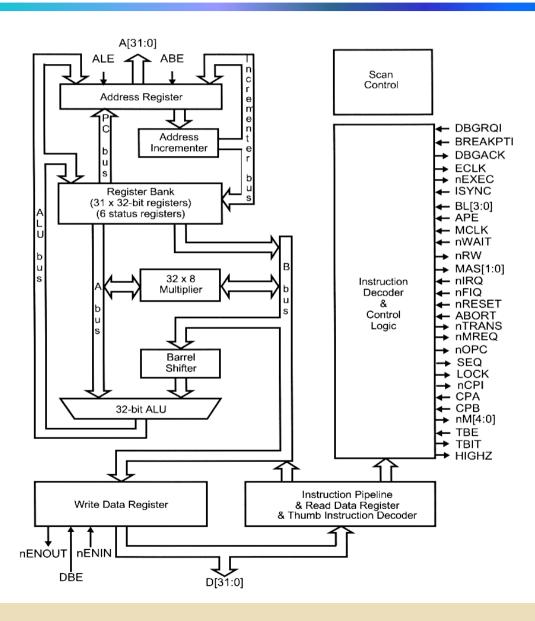

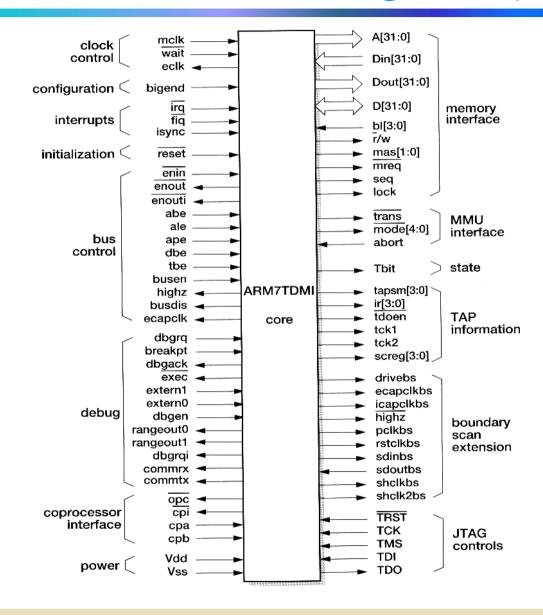

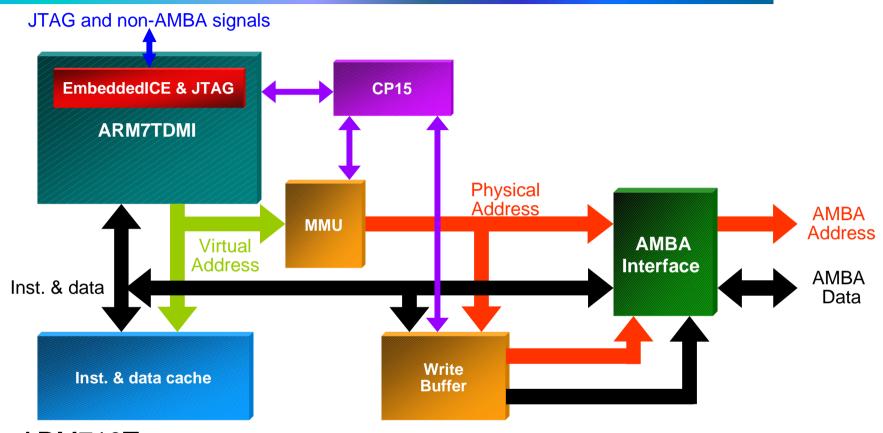

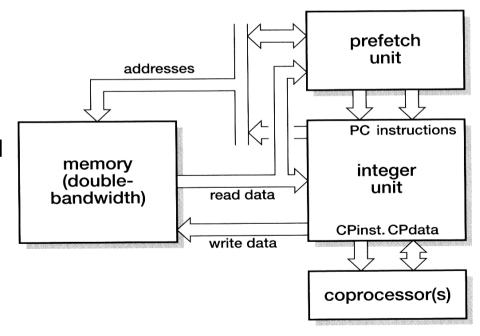

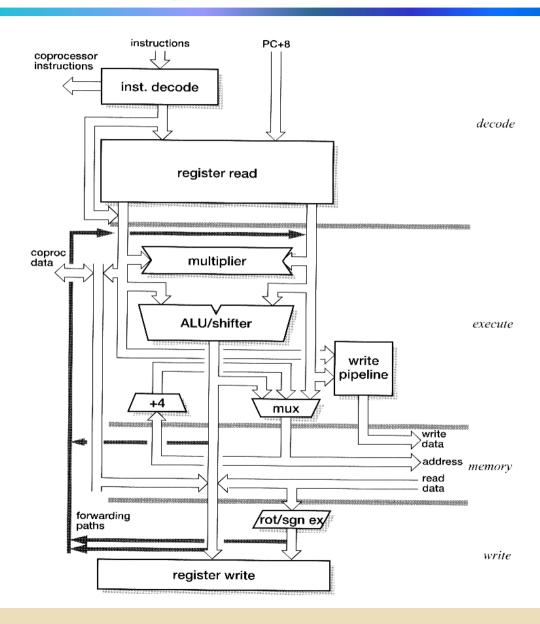

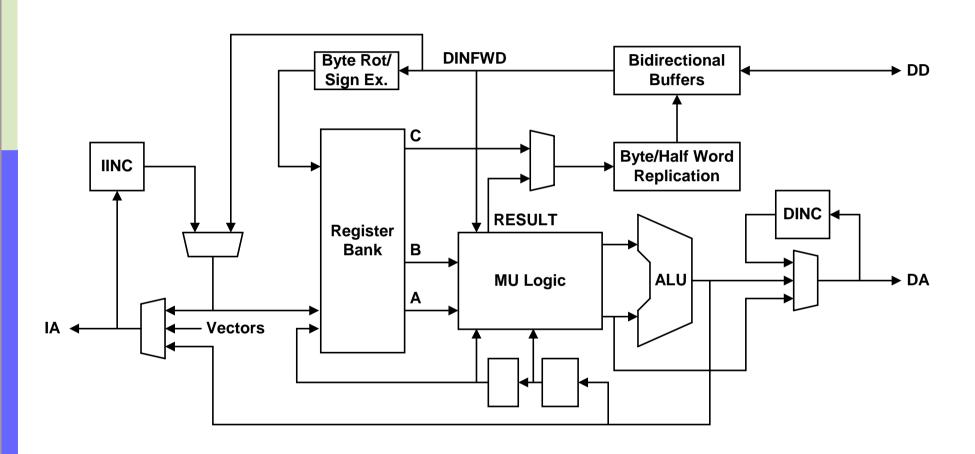

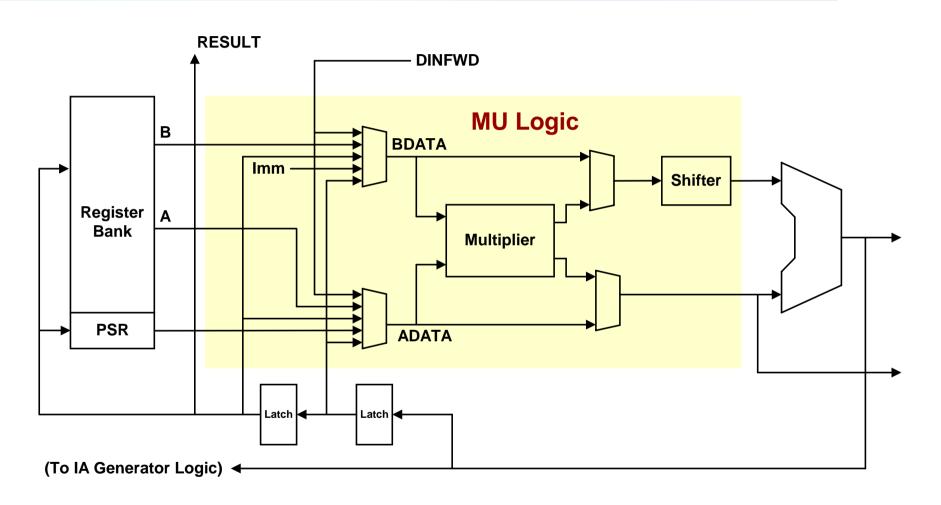

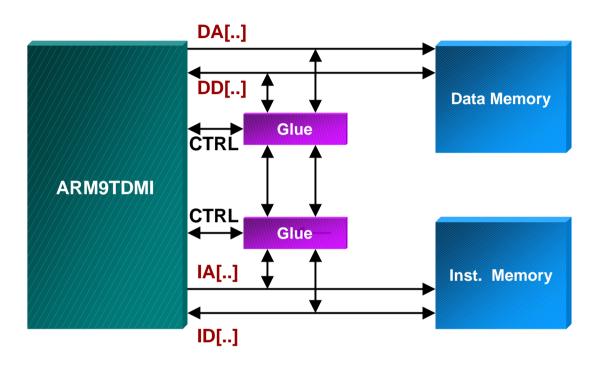

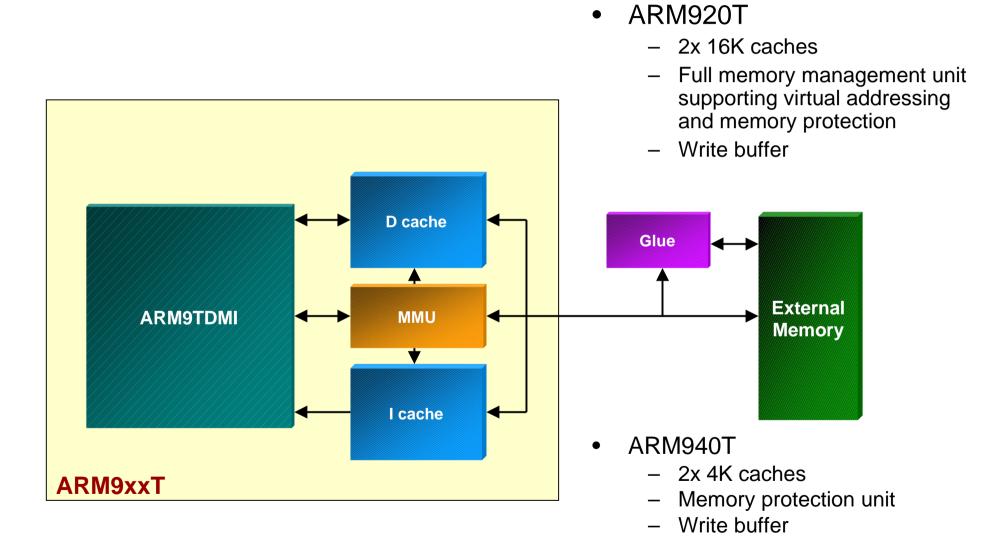

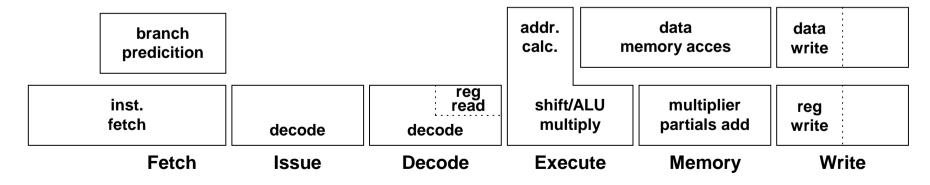

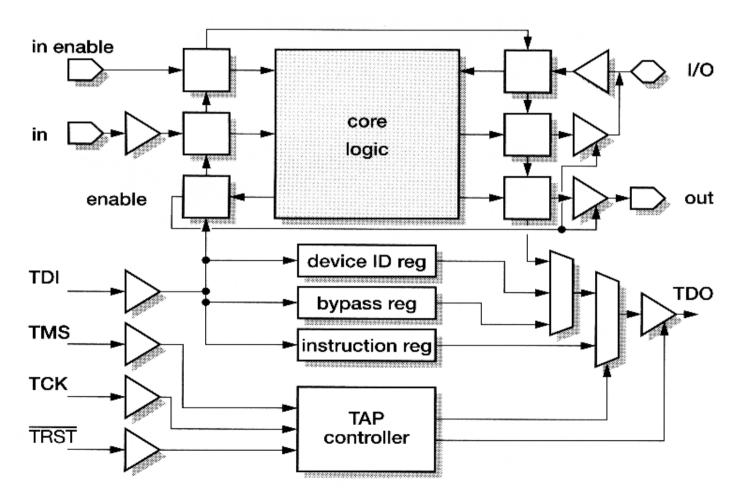

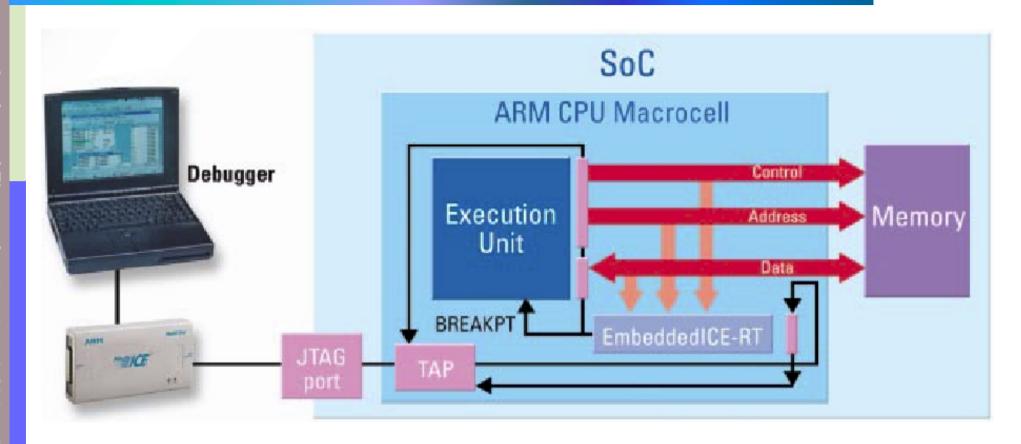

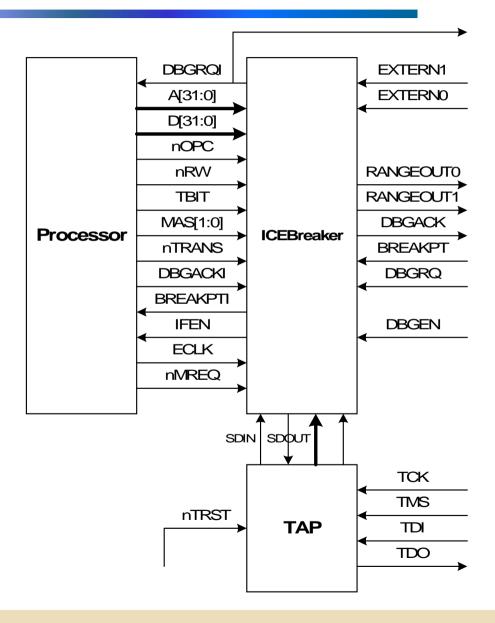

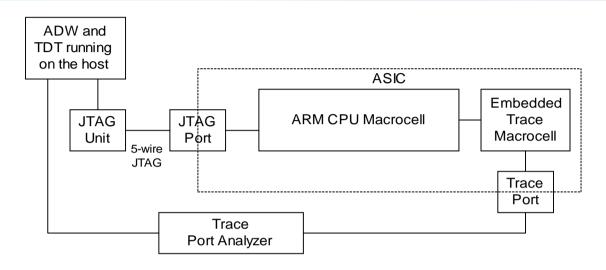

### **ARM Processor Cores**

- ARM Processor core + cache + MMU

→ARM CPU cores

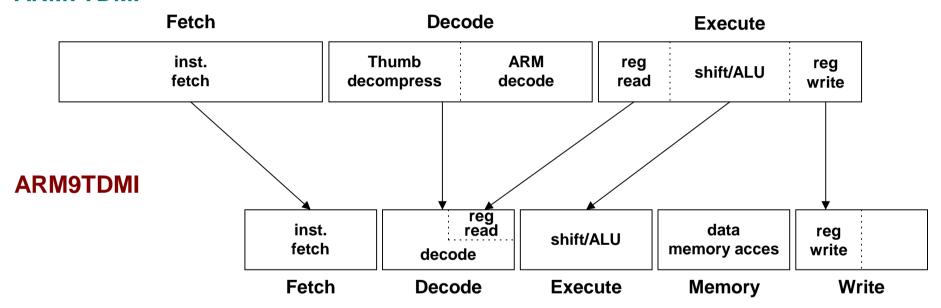

- ARM6 → ARM7 (3V operation, 50-100MHz for .25μ or .18 μ)

T: Thumb 16-bit compressed instruction set

D: on-chip Debug support, enabling the processor to halt in response to a debug request

M: enhanced Multiplier, 64-bit result

I : embedded ICE hardware, give on-chip breakpoint and watchpoint support

### **ARM Processor Cores**

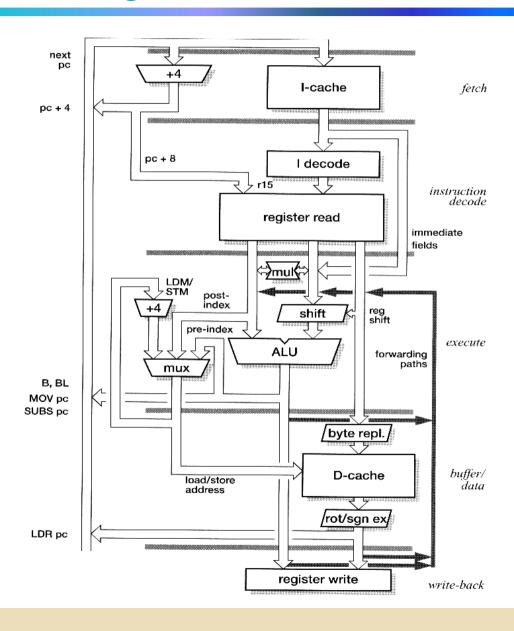

- ARM 8 → ARM 9

- $\rightarrow$  ARM 10

- ARM 9

- 5-stage pipeline (130 MHz or 200MHz)

- using separate instruction and data memory ports

- ARM 10 (1998. Oct.)

- high performance, 300 MHz

- multimedia digital consumer applications

- optional vector floating-point unit

## ARM Architecture Versions (1/5)

#### Version 1

- the first ARM processor, developed at Acorn Computers Limited 1983-1985

- 26-bit addressing, no multiply or coprocessor support

#### Version 2

- sold in volume in the Acorn Archimedes

- 26-bit addressing, including 32-bit result multiply and coprocessor

#### Version 2a

- coprocessor 15 as the system control coprocessor to manage cache

- add the atomic load store (SWP) instruction

## ARM Architecture Versions (2/5)

#### Version 3

- first ARM processor designed by ARM Limited (1990)

- ARM6 (macro cell)

- ARM60 (stand-alone processor)

- ARM600 (an integrated CPU with on-chip cache, MMU, write buffer)

- ARM610 (used in Apple Newton)

- 32-bit addressing, separate CPSR and SPSRs

- add the undefined and abort modes to allow coprocessor emulation and virtual memory support in supervisor mode

#### Version 3M

introduce the signed and unsigned multiply and multiplyaccumulate instructions that generate the full 64-bit result

## ARM Architecture Versions (3/5)

### Version 4

- add the signed, unsigned half-word and signed byte load and store instructions

- reserve some of SWI space for architecturally defined operations

- system mode is introduced

### Version 4T

16-bit Thumb compressed form of the instruction set is introduced

## ARM Architecture Versions (4/5)

- Version 5T

- introduced recently, a superset of version 4T adding the BLX, CLZand BRK instructions

- Version 5TE

- add the signal processing instruction set extension

# ARM Architecture Versions (5/5)

| Core                                | Architecture |

|-------------------------------------|--------------|

| ARM1                                | v1           |

| ARM2                                | v2           |

| ARM2as, ARM3                        | v2a          |

| ARM6, ARM600, ARM610                | v3           |

| ARM7, ARM700, ARM710                | v3           |

| ARM7TDMI, ARM710T, ARM720T, ARM740T | v4T          |

| StrongARM, ARM8, ARM810             | v4           |

| ARM9TDMI, ARM920T, ARM940T          | V4T          |

| ARM9E-S                             | v5TE         |

| ARM10TDMI, ARM1020E                 | v5TE         |

### 32-bit Instruction Set

- ARM assembly language program

- ARM development board or ARM emulator

- ARM instruction set

- standard ARM instruction set

- a compressed form of the instruction set, a subset of the full ARM instruction set is encoded into 16-bit instructions - Thumb instruction

- some ARM cores support instruction set extensions to enhance signal processing capabilities

## Instructions

- Data processing instructions

- Data transfer instructions

- Control flow instructions

# ARM Instruction Set Summary (1/4)

| Mnemonic | Instruction                 | Action                                  |

|----------|-----------------------------|-----------------------------------------|

| ADC      | Add with carry              | Rd:=Rn+Op2+Carry                        |

| ADD      | Add                         | Rd:=Rn+Op2                              |

| AND      | AND                         | Rd:=Rn AND Op2                          |

| В        | Branch                      | R15:=address                            |

| BIC      | Bit Clear                   | Rd:=Rn AND NOT Op2                      |

| BL       | Branch with Link            | R14:=R15                                |

| BX       | Branch and Exchange         | R15:=address<br>R15:=Rn<br>T bit:=Rn[0] |

| CDP      | Coprocessor Data Processing | (Coprocessor-specific)                  |

| CMN      | Compare Negative            | CPSR flags:=Rn+Op2                      |

| CMP      | Compare                     | CPSR flags:=Rn-Op2                      |

# ARM Instruction Set Summary (2/4)

| Mnemonic | Instruction                                    | Action                   |

|----------|------------------------------------------------|--------------------------|

| EOR      | Exclusive OR                                   | Rd:=Rn^Op2               |

| LDC      | Load Coprocessor from memory                   | (Coprocessor load)       |

| LDM      | Load multiple registers                        | Stack Manipulation (Pop) |

| LDR      | Load register from memory                      | Rd:=(address)            |

| MCR      | Move CPU register to coprocessor register      | CRn:=rRn{ <op>cRm}</op>  |

| MLA      | Multiply Accumulate                            | Rd:=(Rm*Rs)+Rn           |

| MOV      | Move register or constant                      | Rd:=Op2                  |

| MRC      | Move from coprocessor register to CPU register | rRn:=cRn{ <op>cRm}</op>  |

| MRS      | Move PSR status/flags to register              | Rn:=PSR                  |

| MSR      | Move register to PSR status/flags              | PSR:=Rm                  |

|          |                                                |                          |

# ARM Instruction Set Summary (3/4)

| Mnemonic | Instruction                          | Action                    |

|----------|--------------------------------------|---------------------------|

| MUL      | Multiply                             | Rd:=Rm*Rs                 |

| MVN      | Move negative register               | Rd:=~Op2                  |

| ORR      | OR                                   | Rd:=Rn OR Op2             |

| RSB      | Reverse Subtract                     | Rd:=Op2-Rn                |

| RSC      | Reverse Subtract with Carry          | Rd:=Op2-Rn-1+Carry        |

| SBC      | Subtract with Carry                  | Rd:=Rn-Op2-1+Carry        |

| STC      | Store coprocessor register to memory | address:=cRn              |

| STM      | Store Multiple                       | Stack manipulation (Push) |

# ARM Instruction Set Summary (4/4)

| Mnemonic | Instruction               | Action                  |

|----------|---------------------------|-------------------------|

| STR      | Store register to memory  | <address>:=Rd</address> |

| SUB      | Subtract                  | Rd:=Rn-Op2              |

| SWI      | Software Interrupt        | OS call                 |

| SWP      | Swap register with memory | Rd:=[Rn]<br>[Rn]:=Rm    |

| TEQ      | Test bitwise equality     | CPSR flags:=Rn EOR Op2  |

| TST      | Test bits                 | CPSR flags:=Rn AND Op2  |

## **ARM Instruction Set Format**

| Data processing/<br>PSRTransfer |

|---------------------------------|

| Multiply                        |

Multiply Long

Single Data Swap

Branch and Exchange

Halfword Data Transfer: register offset

Halfword Data Transfer: immediate offset

Single Data Transfer

Undefined

Block Data Transfer

Branch

Coprocessor Data Transfer

Coprocessor Data Operation

Coprocessor Register Transfer

Software Interrupt

| 31 30 29 20 |   |   |   |   |     |                      |     | 20 | 10  | -10    |     | -10       | 10   | 1-4 | 10 | 12      |           | 10 | Э     | 0     | ,   | 0 | 5      | 4     | 3   | -    | 1 0 |  |  |     |  |  |    |  |  |   |  |    |   |

|-------------|---|---|---|---|-----|----------------------|-----|----|-----|--------|-----|-----------|------|-----|----|---------|-----------|----|-------|-------|-----|---|--------|-------|-----|------|-----|--|--|-----|--|--|----|--|--|---|--|----|---|

| Cond        | 0 | 0 | 1 |   | Opc | ode                  |     | S  |     | Rn     |     |           |      | R   | d  |         | Operand 2 |    |       |       |     |   |        |       |     |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 0 | 0 | 0 | 0 | 0   | 0                    | Α   | s  | Rd  |        |     |           |      | R   | ln |         | Rs 1 0    |    |       |       |     | 0 | 1      |       | n   |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 0 | 0 | 0 | 0 | 1   | U                    | Α   | s  |     | Rd     | lHi |           | RdLo |     |    |         | R         | 'n |       | 1     | 0   | 0 | 1      | Rm    |     |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 0 | 0 | 0 | 1 | 0   | В                    | 0   | 0  |     | Rn     |     |           |      | R   | ld |         | 0         | 0  | 0     | 0     | 1   | 0 | 0      | 1     |     | Rn   | n   |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 0 | 0 | 0 | 1 | 0   | 0                    | 1   | 0  | 1   | 1      | 1   | 1         | 1    | 1   | 1  | 1       | 1         | 1  | 1     | 1     | 0   | 0 | 0      | 1     |     | Rn   | 1   |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 0 | 0 | 0 | Р | U   | 0                    | w   | L  |     | Rn     |     | Rd        |      | 0   | 0  | 0       | 0         | 1  | s     | Н     | 1   |   | Rn     | n     |     |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 0 | 0 | 0 | Р | U   | 1                    | w   | L  |     | Rn     |     |           | Rd   |     |    |         | Offset    |    |       |       | 1   | s | Н      | 1     |     | Offs | et  |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 0 | 1 | Ι | Р | U   | В                    | w   | L  | Rn  |        |     | Rd Offset |      |     |    |         |           |    |       |       |     |   |        |       |     |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 0 | 1 | 1 |   |     |                      |     |    |     |        |     |           | 1    |     |    |         |           |    |       |       |     |   |        |       |     |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 1 | 0 | 0 | Р | U   | s                    | w   | L  | Rn  |        |     |           |      |     |    |         |           | Re | egist | ter L | ist |   |        |       |     |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 1 | 0 | 1 | L |     |                      |     |    |     |        |     |           |      |     |    | Off     | set       |    |       |       |     |   |        |       |     |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 1 | 1 | 0 | Р | U   | N                    | w   | L  |     | Rn CRd |     |           |      |     |    | CRd CP# |           |    |       |       |     |   | Offset |       |     |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 1 | 1 | 1 | 0 |     | СР                   | Орс |    | CRn |        |     | CRn       |      |     | n  |         | CRn       |    | CRn   |       | CRn |   | CRn    |       | CRn |      | CRd |  |  | CP# |  |  | СР |  |  | 0 |  | CR | m |

| Cond        | 1 | 1 | 1 | 0 | С   | ΡO                   | рс  | L  |     | CRn    |     |           | Rd   |     |    | CP#     |           |    |       | СР    |     |   | 1      | 1 CRm |     | m    |     |  |  |     |  |  |    |  |  |   |  |    |   |

| Cond        | 1 | 1 | 1 | 1 |     | Ignored by processor |     |    |     |        |     |           |      |     |    |         |           |    |       |       |     |   |        |       |     |      |     |  |  |     |  |  |    |  |  |   |  |    |   |

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

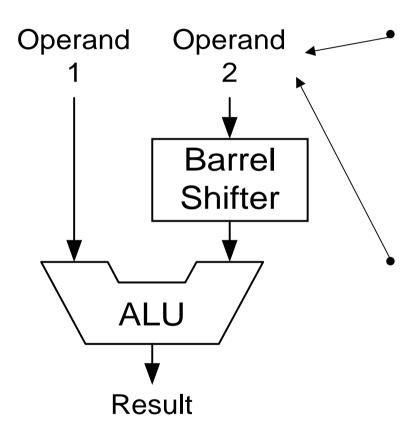

## Data Processing Instructions

- Consist of

- arithmetic (ADD, SUB, RSB)

- logical (BIC, AND)

- compare (CMP, TST)

- register movement (MOV, MVN)

- All operands are 32-bit wide; come from registers or specified as literal in the instruction itself

- Second operand sent to ALU via barrel shifter

- 32-bit result placed in register; long multiply instruction produces 64-bit result

- 3-address instruction format

## **Conditional Execution**

- Most instruction sets only allow branches to be executed conditionally.

- However by reusing the condition evaluation hardware,

ARM effectively increases number of instructions.

- all instructions contain a condition field which determines whether the CPU will execute them

- non-executed instructions still take up 1 cycle

- to allow other stages in the pipeline to complete

- This reduces the number of branches which would stall the pipeline

- allows very dense in-line code

- the time penalty of not executing several conditional instructions is frequently less than overhead of the branch or subroutine call that would otherwise be needed

## **Conditional Execution**

Each of the 16 values causes the instruction to be executed or skipped according to the N, Z, C, V flags in the CPSR

| 31   | 28 | 27 | 0 |

|------|----|----|---|

| cond |    |    |   |

| Opcode [31:28] | Mnemonic extension | Interpretation                      | Status flag state for execution |

|----------------|--------------------|-------------------------------------|---------------------------------|

| 0000           | EQ                 | Equal / equals zero                 | Z set                           |

| 0001           | NE                 | Not equal                           | Z clear                         |

| 0010           | CS/HS              | Carry set / unsigned higher or same | C set                           |

| 0011           | CC/LO              | Carry clear / unsigned lower        | C clear                         |

| 0100           | MI                 | Minus / negative                    | N set                           |

| 0101           | PL                 | Plus / positive or zero             | N clear                         |

| 0110           | VS                 | Overflow                            | V set                           |

| 0111           | VC                 | No overflow                         | V clear                         |

| 1000           | HI                 | Unsigned higher                     | C set and Z clear               |

| 1001           | LS                 | Unsigned lower or same              | C clear or Z set                |

| 1010           | GE                 | Signed greater than or equal        | N equals V                      |

| 1011           | LT                 | Signed less than                    | N is not equal to V             |

| 1100           | GT                 | Signed greater than                 | Z clear and N equals V          |

| 1101           | LE                 | Signed less than or equal           | Z set or N is not equal to V    |

| 1110           | AL                 | Always                              | any                             |

| 1111           | NV                 | Never (do not use!)                 | none                            |

## Using and Updating the Condition Field

- To execute an instruction conditionally, simply postfix it with the appropriate condition:

- for example an add instruction takes the form:

```

• ADD r0,r1,r2 ; r0:=r1+r2 (ADDAL)

```

– to execute this only if the zero flag is set:

```

• ADDEQ r0,r1,r2 ;r0:=r1+r2 iff zero flag is set

```

- By default, data processing operations do not affect the condition flags

- with comparison instructions this is the only effect

- To cause the condition flags to be updated, the S bit of the instruction needs to be set by postfixing the instruction (and any condition code) with an "S".

- for exammple to add two numbers and set the condition flags:

```

• ADDS r0,r1,r2 ; r0:=r1+r2 and set flags

```

# **Data Processing Instructions**

- Simple register operands

- Immediate operands

- Shifted register operands

- Multiply

# Simple Register Operands (1/2)

### Arithmetic Operations

```

ADD r0,r1,r2 ;r0:=r1+r2

ADC r0,r1,r2 ;r0:=r1+r2+C

SUB r0,r1,r2 ;r0:=r1-r2

SBC r0,r1,r2 ;r0:=r1-r2+C-1

RSB r0,r1,r2 ;r0:=r2-r1,reverse subtraction

RSC r0,r1,r2 ;r0:=r2-r1+C-1

```

by default, data processing operations do not affect the condition flags

### Bit-wise Logical Operations

```

AND r0,r1,r2 ;r0:=r1 AND r2

ORR r0,r1,r2 ;r0:=r1 OR r2

EOR r0,r1,r2 ;r0:=r1 XOR r2

BIC r0,r1,r2 ;r0:=r1 AND (NOT r2), bit clear

```

## Simple Register Operands (2/2)

- Register Movement Operations

- omit 1st source operand from the format

```

MOV r0,r2 ;r0:=r2

MVN r0,r2 ;r0:=NOT r2, move 1's complement

```

- Comparison Operations

- not produce result; omit the destination from the format

- just set the condition code bits (N, Z, C and V) in CPSR

## **Immediate Operands**

Replace the second source operand with an immediate operand, which is a literal constant, preceded by "#"

```

ADD r3,r3,#1 ;r3:=r3+1

AND r8,r7,#&FF ;r8:=r7[7:0], &:hexadecimal

```

• Immediate =  $(0~255)*2^{2n}$

## Shifted Register Operands

- ADD r3,r2,r1,LSL#3;r3:=r2+8\*r1

- a single instruction executed in a single cycle

- LSL: Logical shift left by 0 to 31 places, 0 filled at the lsb end

- LSR, ASL(Arithmetic Shift Left), ASR, ROR(Rotate Right), RRX(Rotate Right eXtended by 1 place)

- ADD r5,r5,r3,LSL r2

;r5:=r5+r3\*2<sup>r2</sup>

- MOV r12,r4,ROR r3 ;r12:=r4 rotated right by value of r3

LSL #5

ASR #5, positive operand

ROR #5

LSR #5

ASR #5, negative operand

RRX

## Using the Barrel Shifter: the 2nd Operand

Register, optionally with shift operation applied.

- Shift value can be either:

- 5-bit unsigned integer

- Specified in bottom byte of another register

- Used for multiplication by constant

Immediate value

- 8-bit number, with a range of 0-255

- Rotated right through even number of positions

- Allows increased range of 32-bit constants to be loaded directly into registers

# **Multiply**

MUL r4, r3, r2 ; r4:=

$$(r3*r2)_{[31:0]}$$

## Multiply-Accumulate

MLA

$$r4,r3,r2,r1$$

;  $r4:=(r3*r2+r1)_{[31:0]}$

## Multiplication by a Constant

- Multiplication by a constant equals to a ((power of 2) +/- 1) can be done in a single cycle

- Using MOV, ADD or RSBs with an inline shift

- Example: r0=r1\*5

- Example: r0=r1+(r1\*4)

ADD r0,r1,r1,LSL #2

- Can combine several instructions to carry out other multiplies

- Example: r2=r3\*119

- Example: r2=r3\*17\*7

- Example: r2=r3\*(16+1)\*(8-1)

```

ADD r2,r3,r3,LSL #4 ;r2:=r3*17

RSB r2,r2,r2,LSL #3 ;r2:=r2*7

```

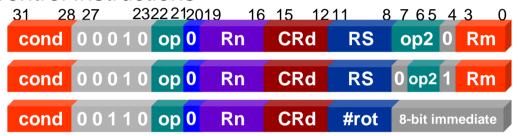

## Data Processing Instructions (1/3)

- <op>{<cond>}{S} Rd,Rn,#<32-bit immediate>

- <op>{<cond>}{S} Rd,Rn,Rm,{<shift>}

- omit Rn when the instruction is monadic (MOV, MVN)

- omit Rd when the instruction is a comparison, producing only condition code outputs (CMP, CMN, TST, TEQ)

- <shift> specifies the shift type (LSL, LSR, ASL, ASR, ROR or RRX)

and in all cases but RRX, the shift amount which may be a 5-bit

immediate (# < # shift>) or a register Rs

#### 3-address format

- 2 source operands and 1 destination register

- one source is always a register, the second may be a register, a shifted register or an immediate value

# Data Processing Instructions (2/3)

| Opcode [24:21] | Mnemonic | Meaning                       | Effect                 |

|----------------|----------|-------------------------------|------------------------|

| 0000           | AND      | Logical bit-wise AND          | Rd := Rn  AND Op2      |

| 0001           | EOR      | Logical bit-wise exclusive OR | Rd := Rn EOR Op2       |

| 0010           | SUB      | Subtract                      | Rd := Rn - Op2         |

| 0011           | RSB      | Reverse subtract              | Rd := Op2 - Rn         |

| 0100           | ADD      | Add                           | Rd := Rn + Op2         |

| 0101           | ADC      | Add with carry                | Rd := Rn + Op2 + C     |

| 0110           | SBC      | Subtract with carry           | Rd := Rn - Op2 + C - 1 |

| 0111           | RSC      | Reverse subtract with carry   | Rd := Op2 - Rn + C - 1 |

| 1000           | TST      | Test                          | See on Rn AND Op2      |

| 1001           | TEQ      | Test equivalence              | See on Rn EOR Op2      |

| 1010           | CMP      | Compare                       | Sec on Rn – Op2        |

| 1011           | CMN      | Compare negated               | Sec on Rn + Op2        |

| 1100           | ORR      | Logical bit-wise OR           | Rd := Rn OR Op2        |

| 1101           | MOV      | Move                          | Rd := Op2              |

| 1110           | BIC      | Bit clear                     | Rd := Rn  AND NOT Op2  |

| 1111           | MVN      | Move negated                  | Rd := NOT Op2          |

## Data Processing Instructions (3/3)

Allows direct control of whether or not the condition codes are affected by S bit (condition code unchanged when S=0)

N=1 if the result is negative; 0 otherwise

(i.e. N=bit 31 of the result)

Z=1 if the result is zero; 0 otherwise

C= carry out from the ALU when ADD, ADC, SUB, SBC, RSB, RSC, CMP, CMN; carry out from the shifter

V=1 if overflow from bit 30 to bit 31; 0 if no overflow

(V is preserved in non-arithmetic operations)

- PC may be used as a source operand (address of the instruction plus

8) except when a register-specified shift amount is used

- PC may be specified as the destination register, the instruction is a form of branch (return from a subroutine)

## Examples

- ADD r5,r1,r3

- ADD Rs,PC, #offset ;PC is ADD address+8

- Decrement r2 and check for zero

```

SUBS r2,r2#1 ;dec r2 and set cc BEQ LABEL

```

Multiply r0 by 5

A subroutine to multiply r0 by 10

```

MOV r0,#3

BL TIMES10

.....

TIMES10 MOV r0,r0,LSL #1 ;*2

ADD r0,r0,r0,LSL #2 ;*5

MOV PC,r14 ;return

```

Add a 64-bit integer in r0, r1 to one in r2, r3

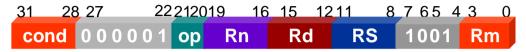

## Multiply Instructions (1/2)

#### 32-bit Product (Least Significant)

```

MUL{<cond>}{S} Rd,Rm,Rs

MLA{<cond>}{S} Rd,Rm,Rs,Rn

```

#### 64-bit Product

| Opcode [23:21] | Mnemonic | Meaning                             | Effect                      |

|----------------|----------|-------------------------------------|-----------------------------|

| 000            | MUL      | Multiply (32-bit result)            | Rd := (Rm * Rs) [31:0]      |

| 001            | MLA      | Multiply-accumulate (32-bit result) | Rd := (Rm * Rs + Rn) [31:0] |

| 100            | UMULL    | Unsigned multiply long              | RdHi:RdLo := Rm * Rs        |

| 101            | UMLAL    | Unsigned multiply-accumulate long   | RdHi:RdLo += Rm * Rs        |

| 110            | SMULL    | Signed multiply long                | RdHi:RdLo := Rm * Rs        |

| 111            | SMLAL    | Signed multiply-accumulate long     | RdHi:RdLo += Rm * Rs        |

## Multiply Instructions (2/2)

- Accumulation is denoted by "+="

- Example: form a scalar product of two vectors

```

MOV r11,#20 ;initialize loop counter

MOV r10,#0 ;initialize total

Loop LDR r0,[r8],#4 ;get first component

LDR r1,[r9],#4 ;get second component

MLA r10,r0,r1,r10

SUBS r11,r11,#1

BNE Loop

```

## Count Leading Zeros (CLZ-V5T only)

### CLZ{<cond>} Rd,Rm

- set Rd to the number of the bit position of the most significant 1 in Rm; If Rm is zero, Rd=32

- useful for renormalizing numbers

### Example

```

MOV r0, #&100

CLZ r1, r0 ;r1:=23

```

### Example

```

CLZ r1,r2

MOVS r2,r2,LSL r1

```

## **Data Transfer Instructions**

- Three basic forms to move data between ARM registers and memory

- single register load and store instruction

- a byte, a 16-bit half word, a 32-bit word

- multiple register load and store instruction

- to save or restore workspace registers for procedure entry and exit

- to copy blocks of data

- single register swap instruction

- a value in a register to be exchanged with a value in memory

- to implement semaphores to ensure mutual exclusion on accesses

## Single Register Data Transfer

Word transfer

```

LDR / STR

```

Byte transfer

```

LDRB / STRB

```

Halfword transfer

```

LDRH / STRH

```

Load singed byte or halfword-load value and sign extended to 32 bits

```

LDRSB / LDRSH

```

All of these can be conditionally executed by inserting the appropriate condition code after STR/LDR

```

LDREQB

```

## Addressing

- Register-indirect addressing

- Base-plus-offset addressing

- base registerr0-r15

- offset, add or subtract an unsigned number immediate register (not PC) scaled register (only available for word and unsigned byte instructions)

- Stack addressing

- Block-copy addressing

## Register-indirect Addressing

Use a value in one register (base register) as a memory address

```

LDR r0,[r1] ;r0:=mem<sub>32</sub>[r1]

STR r0,[r1] ;mem<sub>32</sub>[r1]:=r0

```

- Other forms

- adding immediate or register offsets to the base address

## Initializing an Address Pointer

- A small offset to the program counter, r15

- ARM assembler has a "pseudo" instruction, ADR

- As an example, a program which must copy data from TABLE1 to TABLE2, both of which are near to the code

```

COPY ADR r1, TABLE1; r1 points to TABLE1

ADR r2, TABLE2; r2 points to TABLE2

...

TABLE1

...; <source>

TABLE2

...; <destination>

```

# Single Register Load and Store

A base register, an offset which may be another register or an immediate value

| Copy   | ADR | r1,TABLE1 |

|--------|-----|-----------|

|        | ADR | r2,TABLE2 |

| Loop   | LDR | r0,[r1]   |

|        | STR | r0,[r2]   |

|        | ADD | r1,r1,#4  |

|        | ADD | r2,r2,#4  |

|        | 333 |           |

|        | ••• |           |

| TABLE1 |     |           |

|        | ••• |           |

| TABLE2 |     |           |

|        |     |           |

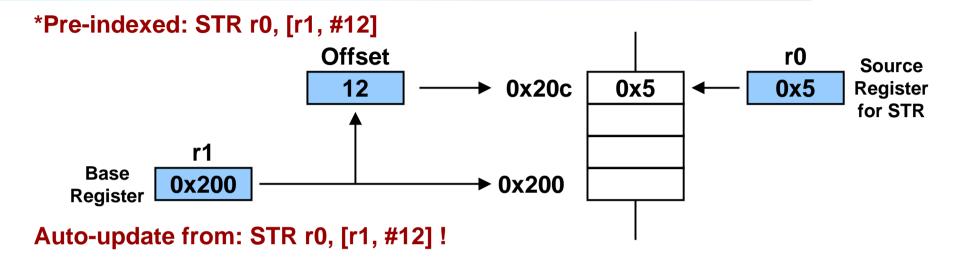

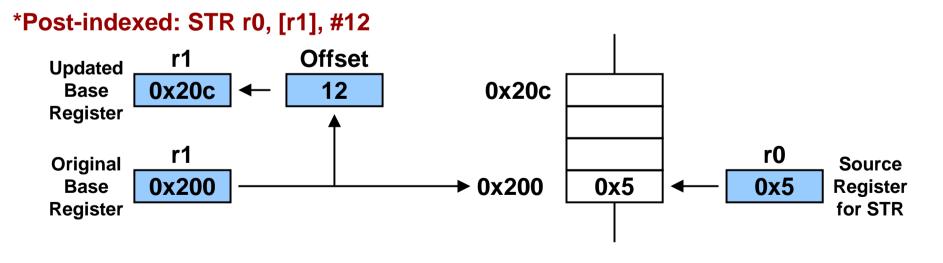

# Base-plus-offset Addressing (1/3)

#### Pre-indexing

```

LDR r0, [r1, #4]; r0:=mem<sub>32</sub>[r1+4]

```

offset up to 4K, added or subtracted, (#-4)

#### Post-indexing

```

LDR r0, [r1], #4 ; r0 := mem_{32}[r1], r1 := r1+4

```

equivalent to a simple register-indirect load, but faster, less code space

#### Auto-indexing

```

LDR r0,[r1,#4]! ;r0:=mem32[r1+4], r1:=r1+4

```

no extra time, auto-indexing performed while the data is being fetched from memory

# Base-plus-offset Addressing (2/3)

# Base-plus-offset Addressing (3/3)

• Copy ADR r1, TABLE1

ADR r2, TABLE2

Loop LDR r0,[r1],#4

STR r0,[r2],#4

333

•••

TABLE1

•••

TABLE 2

•••

A single unsigned byte load

LDRB r0, [r1] ;

$$r0 := mem_8[r1]$$

also support signed bytes, 16-bit half-word

# Loading Constants (1/2)

- No single ARM instruction can load a 32-bit immediate constant directly into a register

- all ARM instructions are 32-bit long

- ARM instructions do not use the instruction stream as data

- The data processing instruction format has 12 bits available for operand 2

- if used directly, this would only give a range of 4096

- Instead it is used to store 8-bit constants, give a range of 0~255

- These 8 bits can then be rotated right through an even number of positions (i.e. RORs by 0,2,4,...,30)

- This gives a much larger range of constants that can be directly loaded, though some constants will still need to be loaded from memory

# Loading Constants (2/2)

This gives us:

| − 0~255             | [0-0xff]                                |

|---------------------|-----------------------------------------|

| - 256,260,264,,1020 | [0x100-0x3fc,step4,0x40-0xff ror 30]    |

| - 1024,1240,,4080   | [0x400-0xff0,step16,0x40-0xff ror 28]   |

| - 4096,4160,,16320  | [0x1000-0x3fc0,step64,0x40-0xff ror 26] |

To load a constant, simply move the required value into a register - the assembler will convert to the rotate form for us

```

- MOV r0, \#4096 ; MOV r0, \#0x1000 (0x40 ror 26)

```

The bitwise complements can also be formed using MVN:

```

- MOV r0,#0xFFFFFFFF ; MVN r0,#0

```

Values that cannot be generated in this way will cause an error

## Loading 32-bit Constants

To allow larger constants to be loaded, the assembler offers a pseudo-instruction:

```

LDR rd, =const

```

- This will either:

- produce a MOV or MVN instruction to generate the value (if possible) or

- generate a LDR instruction with a PC-relative address to read the constant from a *literal pool* (Constant data area embedded in the code)

- For example

As this mechanism will always generate the best instruction for a given case, it is the recommended way of loading constants.

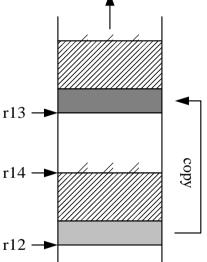

# Multiple Register Data Transfer (1/2)

- The load and store multiple instructions (LDM/STM) allow between 1 and 16 registers to be transferred to or from memory

- order of register transfer cannot be specified, order in the list is insignificant

- lowest register number is always transferred to/from lowest memory location accessed

- The transferred registers can be either

- any subset of the current bank of registers (default)

- any subset of the user mode bank of registers when in a privileged mode (postfix instruction with a "^")

- Base register used to determine where memory access should occur

- 4 different addressing modes

- base register can be optionally updated following the transfer (using "!")

- These instructions are very efficient for

- moving blocks of data around memory

- saving and restoring context stack

# Multiple Register Data Transfer (2/2)

Allow any subset (or all, r0 to r15) of the 16 registers to be transferred with a single instruction

```

LDMIA r1, {r0, r2, r5}

;r0:=mem<sub>32</sub>[r1]

;r2:=mem<sub>32</sub>[r1+4]

;r5:=mem<sub>32</sub>[r1+8]

```

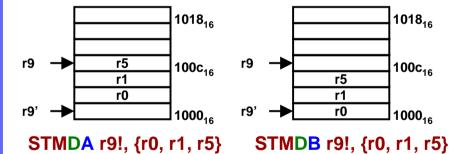

# Stack Processing

- A stack is usually implemented as a linear data structure which grows up (an ascending stack) or down (a descending stack) memory

- A stack pointer holds the address of the current top of the stack, either by pointing to the last valid data item pushed onto the stack (a full stack), or by pointing to the vacant slot where the next data item will be placed (an empty stack)

- ARM multiple register transfer instructions support all four forms of stacks

- full ascending: grows up; base register points to the highest address containing a valid item

- empty ascending: grows up; base register points to the first empty location above the stack

- full descending: grows down; base register points to the lowest address containing a valid data

- empty descending: grows down, base register points to the first empty location below the stack

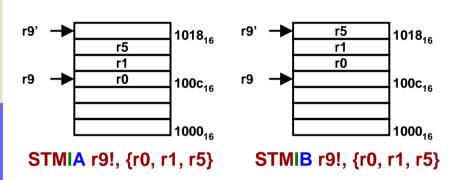

# Block Copy Addressing (1/2)

#### Addressing modes

|           |        | Ascending      |                | Descending     |                |

|-----------|--------|----------------|----------------|----------------|----------------|

|           |        | Full           | Empty          | Full           | Empty          |

| Increment | Before | STMIB<br>STMFA |                |                | LDMIB<br>LDMED |

|           | After  |                | STMIA<br>STMEA | LDMIA<br>LDMFD |                |

| Decrement | Before |                | LDMDB<br>LDMEA | STMDB<br>STMFD |                |

|           | After  | LDMDA<br>LDMFA |                |                | STMDA<br>STMED |

# Block Copy Addressing (2/2)

Copy 8 words from the location r0 points to to the location r1 points to

```

LDMIA r0!, {r2-r9}

STMIA r1, {r2-r9}

```

- r0 increased by 32, r1 unchanged

- If r2 to r9 contained useful values, preserve them by pushing them onto a stack

```

STMFD r13!, {r2-r9}

LDMIA r0!, {r2-r9}

STMIA r1, {r2-r9}

LDMFD r13, {r2-r9}

```

FD postfix: full descending stack addressing mode

# Memory Block Copy

The direction that the base pointer moves through memory is given by the postfix to the STM/LDM instruction increasing

```

- STMIA/LDMIA: Increment After

```

- STMIB/LDMIB: Increment Before

- STMDA/LDMDA: Decrement After

- STMDB/LDMDB: Decrement Before

#### For Example

```

;r12 points to start of source data

;r14 points to end of source data

;r13 points to start of destination data

Loop LDMIA r12!,{r0-r11} ;load 48 bytes

STMIA r13!,{r0-r11} ;and store them

CMP r12,r14 ;check for the end

BNE Loop ;and loop until done

```

- this loop transfers 48 bytes in 31 cycles

- over 50Mbytes/sec at 33MHz

memory

# Single Word and Unsigned Byte Data Transfer Instructions

Pre-indexed form

```

LDR | STR { < cond > } {B} Rd, [Rn, < offset > ] {!}

```

Post-index form

PC-relative form

```

LDR | STR { < cond > } {B} Rd, LABEL

```

- LDR: 'load register'; STR: 'store register'

- 'B' unsigned byte transfer, default is word;

- <offset> may be # +/-<12-bit immediate> or +/- Rm {, shift}

- ! auto-indexing

- T flag selects the user view of the memory translation and protection system

# Example

Store a byte in r0 to a peripheral

```

LDR r1, UARTADD ; UART address into r1

STRB r0, [r1] ; store data to UART

...

UARTADD & &10000000 ; address literal

```

### Half-word and Signed Byte Data Transfer Instructions

Pre-indexed form

```

LDR | STR { < cond > } H | SH | SB Rd, [Rn, < offset > ] {!}

```

Post-indexed form

```

LDR | STR { < cond > } H | SH | SB Rd, [Rn], < offset >

```

- <offset> is # +/-<8-bit immediate> or +/-Rm

- H|SH|SB selects the data type

- unsigned half-word

- signed half-word and

- signed byte

- Otherwise the assemble format is for word and unsigned byte transfer

# Example

Expand an array of signed half-words into an array of words

```

r1,ARRAY1 ;half-word array start

ADR

ADR

r2,ARRAY2

;word array start

ADR

r3,ENDARR1

;ARRAY1 end+2

LDRSH r0,[r1],#2 ;get signed half-word

Loop

STR

r0,[r2],#4

; save word

CMP

r1,r3

;check for end of array

BLT

Loop ; if not finished, loop

```

## Multiple Register Transfer Instructions

- LDM|STM {<cond>}<add mode> Rn{!},<registers>

- <add mode> specifies one of the addressing modes

- '!': auto-indexing

- <registers> a list of registers, e.g., {r0, r3-r7, pc}

- In non-user mode, the CPSR may be restored by LDM{<cond>}<add mode> Rn{!},<registers+PC>^

- In non-user mode, the user registers may be saved or restored by

```

LDM | STM { < cond > } < add mode > Rn, < registers - PC > ^

```

The register list must not contain PC and write-back is not allowed

# Example

Save 3 work registers and the return address upon entering a subroutine (assume r13 has been initialized for use as a stack pointer)

```

STMFD r13!, {r0-r2,r14}

```

Restore the work registers and return

## Swap Memory and Register Instructions

- SWP{<cond>}{B} Rd,Rm,[Rn]

- Rd <- [Rn], [Rn] <- Rm

- Combine a load and a store of a word or an unsigned byte in a single instruction

- Example

```

ADR r0, SEMAPHORE

SWPB r1, r1, [r0] ; exchange byte

```

# Status Register to General Register Transfer Instructions

- MRS{<cond>} Rd,CPSR|SPSR

- The CPSR or the current mode SPSR is copied into the destination register. All 32 bits are copied.

- Example

```

MRS r0,CPSR

MRS r3,SPSR

```

# General Register to Status Register Transfer Instructions

- MSR{<cond>} CPSR\_<field>|SPSR\_<field>,#<32-bit immediate>

MSR{<cond>} CPSR\_<field>|SPSR\_<field>,Rm

- <field> is one of

- c the control field PSR[7:0]

- x the extension field PSR[15:8]

- s the status field PSR[23:16]

- f the flag field PSR[31:24]

#### Example

```

set N, X, C, V flags

```

MSR CPSR\_f, #&f000000

set just C, preserving N, Z, V

```

MRS r0,CPSR

ORR r0,r0,#&20000000 ;set bit29 of r0

MSR CPSR f,r0

```

#### **Control Flow Instructions**

- Branch instructions

- Conditional branches

- Conditional execution

- Branch and link instructions

- Subroutine return instructions

- Supervisor calls

- Jump tables

## **Branch Instructions**

B LABEL

•••

LABEL ..

LABEL comes after or before the branch instruction

#### **Conditional Branches**

The branch has a condition associated with it and it is only executed if the condition codes have the correct value taken or not taken

```

MOV r0,#0 ;initialize counter

Loop ...

ADD r0,r0,#1 ;increment loop counter

CMP r0,#10 ;compare with limit

BNE Loop ;repeat if not equal

;else fall through

```

## **Conditional Branch**

| Branch | Interpretation   | Normal uses                                       |      |

|--------|------------------|---------------------------------------------------|------|

| В      | Unconditional    | Always take this branch                           |      |

| BAL    | Always           | Always take this branch                           |      |

| BEQ    | Equal            | Comparison equal or zero result                   |      |

| BNE    | Not Equal        | Comparison equal or non-zero result               |      |

| BPL    | Plus             | Result positive or zero                           |      |

| BMI    | Minus            | Result minus or negative                          |      |

| BCC    | Carry clear      | Arithmetic operation did not give carry-out       |      |

| BLO    | Lower            | Unsigned comparison gave lower                    |      |

| BCS    | Carry set        | Arithmetic operation gave give carry-out          |      |

| BHS    | Higher or same   | Unsigned comparison gave higher or same           | 1    |

| BVC    | Overflow clear   | Signed integer operation; no overflow occurred    | <br> |

| BVS    | Overflow set     | Signed integer operation; overflow occurred       |      |

| BGT    | Greater than     | Signed integer comparison gave greater than       | {    |

| BGE    | Greater or equal | Signed integer comparison gave greater or equal   | k    |

| BLT    | Less than        | Signed integer comparison gave less than          |      |

| BLE    | Less or equal    | Signed integer comparison gave less than or equal |      |

| BHI    | Higher           | Unsigned comparison gave higher                   |      |

| BLS    | Lower or same    | Unsigned comparison gave lower or same            |      |

|        |                  |                                                   |      |

#### Note:

The pair listed in the same row →

Synonyms, identical binary code

### **Conditional Execution**

An unusual feature of the ARM instruction set is that conditional execution applies not only to branches but to all ARM instructions

```

CMP r0,#5

BEQ Bypass ;if(r0!=5)

ADDNE r1,r1,r0

SUB r1,r1,r2

Bypass ...

CMP r0,#5

ADDNE r1,r1,r0

SUBNE r1,r1,r2

```

• Whenever the conditional sequence is 3 instructions or fewer it is better (smaller and faster) to exploit conditional execution than to use a branch

```

if((a==b)&&(c==d)) e++; CMP r0,r1

CMPEQ r2,r3

ADDEO r4,r4,\#1

```

#### **Branch and Link Instructions**

Perform a branch, save the address following the branch in the link register, r14

```

BL SUBR ;branch to SUBR

... ;return here

SUBR ... ;subroutine entry point

MOV PC,r14 ;return

```

For nested subroutine, push r14 and some work registers required to be saved onto a stack in memory

```

BL SUB1

...

SUB1 STMFD r13!,{r0-r2,r14}; save work and link regs

BL SUB2

...

SUB2

...

```

#### Subroutine Return Instructions

```

SUB ...

MOV PC,r14 ;copy r14 into r15 to return

```

Where the return address has been pushed onto a stack

```

SUB1 STMFD r13!, {r0-r2,r14} ;save work regs and link

BL SUB2

...

LDMFD r13!, {r0-e12,PC} ;restore work regs & return

```

# Supervisor Calls

- The supervisor is a program which operates at a privileged level, which means that it can do things that a user-level program cannot do directly (e.g. input or output)

- SWI instruction

- software interrupt or supervisor call

```

SWI SWI_WriteC ;output r0[7:0]

SWI SWI_Exit ;return to monitor program

```

# Jump Tables

To call one of a set of subroutines, the choice depending on a value computed by the program

```

BI JUMPTAB

BL JUMPTAB

JUMPTAB

CMP r0, #0

JUMPTAB

ADR r1, SUBTAB; r1->SUBTAB

CMP r0, #SUBMAX

;check for overrun

BEQ SUB0

LDRLS PC,[r1,r0,LSL#2]; if OK, table jump

CMP r0,#1

BEQ SUB1

B ERROR

CMP r0, #2

SUBTAB DCD SUB0

BEO SUB2

DCD SUB1

DCD SUB2

```

• The 'DCD' directive instructs the assembler to reserve a word of store and to initialize it to the value of the expression to the right, which in these cases is just the address of the label.

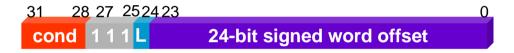

### Branch and Branch with Link (B,BL)

- B{L}{<cond>} <target address>

- <target address> is normally a label in the assembler code.

24-bit offset, sign-extended, shift left 2 places

+ PC (address of branch instruction + 8)

target address

# **Examples**

Unconditional jump

B LABEL ...

Loop ten times

MOV r0,#10 Loop... SUBS r0,#1 BNE Loop

Call a subroutine

BL SUB

...

SUB ...

MOV PC,r14

Conditional subroutine call

CMP r0, #5

BLLT SUB1 ; if r0<5, call SUB1

BLGE SUB2 ; else call SUB2

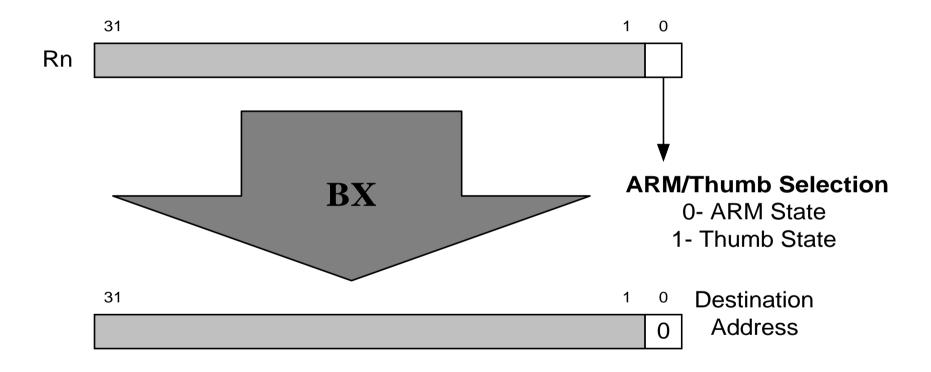

## Branch, Branch with Link and eXchange

- $B\{L\}X\{<cond>\}$  Rm

- the branch target is specified in a register, Rm

- bit[0] of Rm is copied into the T bit in CPSR; bit[31:1] is moved into

PC

- if Rm[0] is 1, the processor switches to execute Thumb instructions and begins executing at the address in Rm aligned to a half-word boundary by clearing the bottom bit

- if Rm[0] is 0, the processor continues executing ARM instructions and begins executing at the address in Rm aligned to a word boundary by clearing Rm[1]

- BLX <target address>

- call Thumb subroutine from ARM

- the H bit (bit 24) is also added into bit 1 of the resulting address, allowing an odd half-word address to be selected for the target instruction which will always be a Thumb instruction

# Example

#### A call to a Thumb subroutine

```

CODE32

...

BLX TSUB ; call Thumb subroutine

...

CODE16 ; start of Thumb code

TSUB ...

BX r14 ; return to ARM code

```

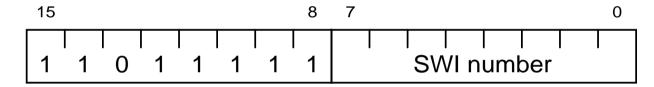

## Software Interrupt (SWI)

- SWI{<cond>} <24-bit immediate>

- used for calls to the operating system and is often called a "supervisor call"

- it puts the processor into supervisor mode and begins executing instruction from address 0x08

- Save the address of the instruction after SWI in r14\_svc

- Save the CPSR in SPSR\_svc

- Enter supervisor mode and disable IRQs by setting CPSR[4:0] to 10011<sub>2</sub> and CPSR[7] to 1

- Set PC to 08<sub>16</sub> and begin executing the instruction there

- the 24-bit immediate does not influence the operation of the instruction but may be interpreted by the system code

## **Examples**

Output the character 'A'

```

MOV r0,#'A'

SWI SWI_WriteC

```

Finish executing the user program and return to the monitor

```

SWI SWI_Exit

```

A subroutine to output a text string

```

BL STROUT

= "Hello World",&0a,&0d,0

...

STROUT LDRB r0,[r14],#1 ;get character

CMP r0,#0 ;check for end marker

SWINE SWI_WriteC ;if not end, print

BNE STROUT ; ... , loop

ADD r14,#3 ;align to next word

BIC r14,#3

MOV PC,r14 ;return

```

## Coprocessor Instructions

- Extend the instruction set through the addition of coprocessors

- System Coprocessor: control on-chip function such as cache and memory management unit

- Floating-point Coprocessor

- Application-Specific Coprocessor

- Coprocessors have their own private register sets and their state is controlled by instructions that mirror the instructions that control ARM registers

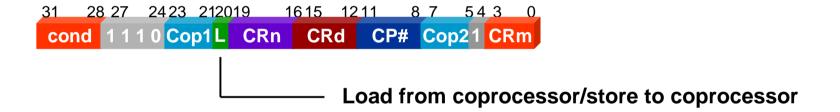

## Coprocessor Data Operations

• CDP{<cond>}<CP#>,<Cop1>,CRd,CRn,CRm{,<Cop2>}

```

31 28 27 2423 2019 1615 1211 8 7 54 3 0 cond 1 1 1 0 Cop1 CRn CRd CP# Cop20 CRm

```

- Use to control internal operations on data in coprocessor registers

- CP# identifies the coprocessor number

- Cop1, Cop2 operation

- Examples

```

CDP P2,3,C0,C1,C2

CDPEQ P3,6,C1,C5,C7,4

```

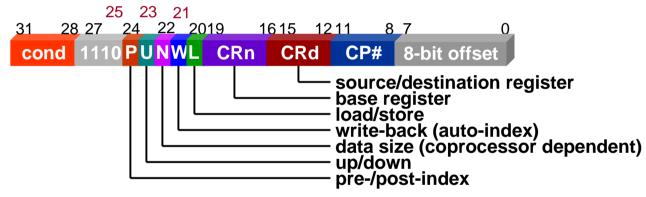

#### Coprocessor Data Transfers

Pre-indexed form

Post-indexed form

- L flag, if present, selects the long data type

- <offset> is # +/-<8-bit immediate>

- the number of words transferred is controlled by the coprocessor

- address calculated within ARM; number of words transferred controlled by the coprocessor

- Examples

```

LDC P6,c0,[r1]

STCEQL P5,c1,[r0],#4

```

#### Coprocessor Register Transfers

Move to ARM register from coprocessor

```

MRC{<cond>} <CP#>,<Cop1>,Rd,CRn,CRm,{,<Cop2>}

```

Move to coprocessor from ARM register

```

MCR{<cond>} <CP#>,<Cop1>,Rd,CRn,CRm,{,<Cop2>}

```

Examples

```

MCR P14,3,r0,c1,c2

MRCCS P2,4,r3,c3,c4,6

```

### Breakpoint Instructions (BKPT-v5T only)

- BKPT <16-bit immediate>

- Used for software debugging purposes; they cause the processor to break from normal instruction execution and enter appropriate debugging procedures

- BKPT is unconditional

- Handled by an exception handler installed on the prefetch abort vector

## **Unused Instruction Space**

Unused Arithmetic Instructions

Unused Control Instructions

Unused Load/Store Instructions

Unused Coprocessor Instructions

Undefined Instruction Space

#### 16-bit Instruction Set

# Thumb Instruction Set (1/3)

| Mnemonic | Instruction            | Lo<br>Register | Hi<br>Register | Condition<br>Code |

|----------|------------------------|----------------|----------------|-------------------|

| ADC      | Add with carry         |                | <b>J</b>       |                   |

| ADD      | Add                    |                |                |                   |

| AND      | AND                    |                |                |                   |

| ASR      | Arithmetic Shift Right |                |                |                   |

| В        | Branch                 |                |                |                   |

| Bxx      | Conditional Branch     |                |                |                   |

| BIC      | Bit Clear              |                |                |                   |

| BL       | Branch with Link       |                |                |                   |

| BX       | Branch and Exchange    |                |                |                   |

| CMN      | Compare Negative       |                |                |                   |

| CMP      | Compare                |                |                |                   |

| EOR      | EOR                    |                |                |                   |

| LDMIA    | Load Multiple          |                |                |                   |

| LDR      | Load Word              |                |                |                   |

# Thumb Instruction Set (2/3)

| Mnemonic | Instruction            | Lo<br>Register | Hi<br>Register | Condition<br>Code |

|----------|------------------------|----------------|----------------|-------------------|

| LDRB     | Load Byte              |                | <b>-</b>       |                   |

| LDRH     | Load Halfword          |                |                |                   |

| LSL      | Logical Shift Left     |                |                |                   |

| LDSB     | Load Signed Byte       |                |                |                   |

| LDSH     | Load Signed Halfword   |                |                |                   |

| LSR      | Logical Shift Right    |                |                |                   |

| MOV      | Move Register          |                |                |                   |

| MUL      | Multiply               |                |                |                   |

| MVN      | Move Negative Register |                |                |                   |

| NEG      | Negate                 |                |                |                   |

| ORR      | OR                     |                |                |                   |

| POP      | Pop Registers          |                |                |                   |

| PUSH     | Push Registers         |                |                |                   |

| ROR      | Rotate Right           |                |                |                   |

# Thumb Instruction Set (3/3)

| Mnemonic | Instruction         | Lo<br>Register | Hi<br>Register | Condition Code |

|----------|---------------------|----------------|----------------|----------------|

| SBC      | Subtract with Carry |                | •              |                |

| STMIA    | Store Multiple      |                |                |                |

| STR      | Store Word          |                |                |                |

| STRB     | Store Byte          |                |                |                |

| STRH     | Store Halfword      |                |                |                |

| SWI      | Software Interrupt  |                |                |                |

| SUB      | Subtract            |                |                |                |

| TST      | Test Bits           |                |                |                |

## Thumb Instruction Format

|    | 15 | 14 | 13 | 12 | 11 | 10      | 9  | 8     | 7     | 6       | 5       | 4     | 3      | 2 1   | 0  |                                            |                                    |

|----|----|----|----|----|----|---------|----|-------|-------|---------|---------|-------|--------|-------|----|--------------------------------------------|------------------------------------|

| 1  | 0  | 0  | 0  |    | p  |         | 0  | ffset | 5     |         |         | Rs    |        | Rd    |    | Move shifted register                      |                                    |

|    |    |    |    | _  |    | -       |    |       |       |         |         |       |        |       |    |                                            |                                    |

| 2  | 0  | 0  | 0  | 1  | 1  | 1       | Ор | Rn    | offs. | et3     |         | Rs    |        | Rd    |    | Add/subtract                               |                                    |

| 3  | 0  | 0  | 1  | Ор |    | Rd      |    |       |       |         | Offset8 |       |        |       |    | Move/compare/add<br>/subtract immediate    |                                    |

| 4  | 0  | 1  | 0  | 0  | 0  | 0       |    | С     | р     |         |         | Rs    |        | Rd    |    | ALU operations                             |                                    |

| 5  | 0  | 1  | 0  | 0  | 0  | 1       | C  | р     | H1    | H2      | R       | Rs/Hs | 3      | Rd/F  | ld | Hi register operations<br>/branch exchange |                                    |

| 6  | 0  | 1  | 0  | 0  | 1  |         | Rd |       |       |         |         | Wo    | rd8    |       |    | PC-relative load                           |                                    |

| 7  | 0  | 1  | 0  | 1  | L  | В       | 0  | Ro    |       | 0       |         | Ro    |        | Rb Rd |    |                                            | Load/store with register<br>offset |

| 8  | 0  | 1  | 0  | 1  | Н  | S       | 1  |       | Ro    |         |         | Rb    |        | Rd    |    | Load/store sign-extended<br>byte/halfword  |                                    |

| 9  | 0  | 1  | 1  | В  | L  |         | С  | ffse  | t5    |         |         | Rb    |        | Rd    |    | Load/store with immediate<br>offset        |                                    |

| 10 | 1  | 0  | 0  | 0  | L  | Offset5 |    |       |       | 5 Rb Rd |         |       |        |       |    | Load/store halfword                        |                                    |

| 11 | 1  | 0  | 0  | 1  | L  |         | Rd |       |       |         |         | Wo    | rd8    |       |    | SP-relative load/store                     |                                    |

| 12 | 1  | 0  | 1  | 0  | SP |         | Rd |       |       |         |         | Wo    | rd8    |       |    | Load address                               |                                    |

| 13 | 1  | 0  | 1  | 1  | 0  | 0       | 0  | 0     | s     |         |         | SI    | Norce. | 17    |    | Add offset to stack pointer                |                                    |

| 14 | 1  | 0  | 1  | 1  | L  | 1       | 0  | R     |       |         |         | RI    | st     |       |    | Push/pop registers                         |                                    |

| 15 | 1  | 1  | 0  | 0  | L  | Rb      |    |       |       |         |         | RI    | ist    |       |    | Multiple load/store                        |                                    |

| 16 | 1  | 1  | 0  | 1  |    | Cond    |    |       |       |         |         | Soff  | set8   |       |    | Conditional branch                         |                                    |

| 17 | 1  | 1  | 0  | 1  | 1  | 1       | 1  | 1     |       | Value8  |         |       |        |       |    | Software Interrupt                         |                                    |

| 18 | 1  | 1  | 1  | 0  | 0  |         |    |       |       | 0       | ffset   | 11    |        |       |    | Unconditional branch                       |                                    |

| 19 | 1  | 1  | 1  | 1  | Н  |         |    |       |       | (       | Offse   | t     |        |       |    | Long branch with link                      |                                    |

|    | 15 | 14 | 13 | 12 | 11 | 10      | 9  | 8     | 7     | 6       | 5       | 4     | 3      | 2 1   | 0  |                                            |                                    |

#### Thumb-ARM Difference

- Thumb instruction set is a subset of the ARM instruction set and the instructions operate on a restricted view of the ARM registers

- Most Thumb instructions are executed unconditionally (All ARM instructions are executed conditionally)

- Many Thumb data processing instructions use a 2-address format, i.e. the destination register is the same as one of the source registers (ARM data processing instructions, with the exception of the 64-bit multiplies, use a 3-address format)

- Thumb instruction formats are less regular than ARM instruction formats => dense encoding

### Register Access in Thumb

- Not all registers are directly accessible in Thumb

- Low register r0~r7: fully accessible

- High register r8~r12: only accessible with MOV, ADD, CMP; only CMP sets the condition code flags

- **SP**(stack pointer), **LR**(link register) & **PC**(program counter): limited accessibility, certain instructions have implicit access to these

- CPSR: only indirect access

- SPSR: no access

# Thumb Accessible Registers

#### **Branches**

- Thumb defines three PC-relative branch instructions, each of which have different offset ranges

- Offset depends upon the number of available bits

- Conditional Branches

- B<cond> label

- 8-bit offset: range of -128 to 127 instructions (+/-256 bytes)

- Only conditional Thumb instructions

- Unconditional Branches

- B label

- 11-bit offset: range of -1024 to 1023 instructions (+/- 2Kbytes)

- Long Branches with Link

- BL subroutine

- Implemented as a pair of instructions

- 22-bit offset: range of -2097152 to 2097151 instructions (+/- 4Mbytes)

## Data Processing Instructions

- Subset of the ARM data processing instructions

- Separate shift instructions (e.g. LSL, ASR, LSR, ROR)

```

LSL Rd,Rs,#Imm5 ;Rd:=Rs <shift> #Imm5

ASR Rd,Rs ;Rd:=Rd <shift> Rs

```

- Two operands for data processing instructions

- act on low registers

```

BIC Rd,Rs ;Rd:=Rd AND NOT Rs

ADD Rd,#Imm8 ;Rd:=Rd+#Imm8

```

also three operand forms of add, subtract and shifts

```

ADD Rd,Rs,#Imm3 ;Rd:=Rs+#Imm3

```

Condition code always set by low register operations

## Load or Store Register

- Two pre-indexed addressing modes

- base register+offset register

- base register+5-bit offset, where offset scaled by

- 4 for word accesses (range of 0-124 bytes / 0-31 words)

- STR Rd, [Rb, #Imm7]

- 2 for halfword accesses (range of 0-62 bytes / 0-31 halfwords)

- LDRH Rd, [Rb, #Imm6]

- 1 for byte accesses (range of 0-31 bytes)

- LDRB Rd, [Rb, #Imm5]

#### Special forms:

- load with PC as base with 1Kbyte immediate offset (word aligned)

- used for loading a value from a literal pool

- load and store with SP as base with 1Kbyte immediate offset (word aligned)

- used for accessing local variables on the stack

#### **Block Data Transfers**

- Memory copy, incrementing base pointer after transfer

- STMIA Rb!, {Low Reg list}

LDMIA Rb!, {Low Reg list}

- Full descending stack operations

- PUSH {Low Reg list}PUSH {Low Reg list, LR}POP {Low Reg list}POP {Low Reg list, PC}

- The optional addition of the LR/PC provides support for subroutine entry/exit.

#### Miscellaneous

- Thumb SWI instruction format

- same effect as ARM, but SWI number limited to 0~255

- syntax:

- SWT <SWT number>

- Indirect access to CPSR and no access to SPSR, so no MRS or MSR instructions

- No coprocessor instruction space

## Thumb Instruction Entry and Exit

#### T bit, bit 5 of CPSR

- if T=1, the processor interprets the instruction stream as 16-bit

Thumb instruction

- if T=0, the processor interprets it as standard ARM instructions

#### Thumb Entry

- ARM cores startup, after reset, executing ARM instructions

- executing a Branch and Exchange instruction (BX)

- set the T bit if the bottom bit of the specified register was set

- switch the PC to the address given in the remainder of the register

#### Thumb Exit

executing a Thumb BX instruction

## The Need for Interworking

- The code density of Thumb and its performance from narrow memory make it ideal for the bulk of C code in many systems. However there is still a need to change between ARM and Thumb state within most applications:

- ARM code provides better performance from wide memory

- therefore ideal for speed-critical parts of an application

- some functions can only be performed with ARM instructions, e.g.

- access to CPSR (to enable/disable interrupts & to change mode)

- access to coprocessors

- exception Handling

- ARM state is automatically entered for exception handling, but system specification may require u;sage of Thumb code for main handler

- simple standalone Thumb programs will also need an ARM assembler header to change state and call the Thumb routine

## Interworking Instructions

- Interworking is achieved using the Branch Exchange instructions

- in Thumb stateBX Rn

- in ARM state (on Thumb-aware cores only)

BX<condition> Rn

where Rn can be any registers (r0 to r15)

- This performs a branch to an absolute address in 4GB address space by copying Rn to the program counter

- Bit 0 of Rn specifies the state to change to

# Switching between States

# Example

```

istart off in ARM state

CODE 32

ADR r0, Into Thumb+1; generate branch target

;address & set bit 0,

; hence arrive Thumb state

BX r0

; branch exchange to Thumb

CODE 16

;assemble subsequent as

; Thumb

Into Thumb

; generate branch target to

ADR r5, Back_to_ARM

;word-aligned address,

;hence bit 0 is cleared.

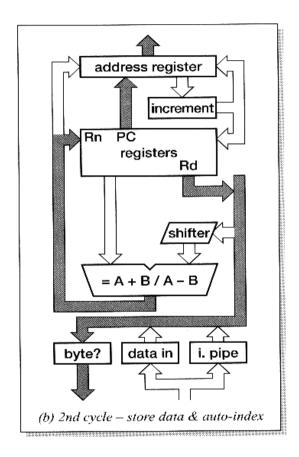

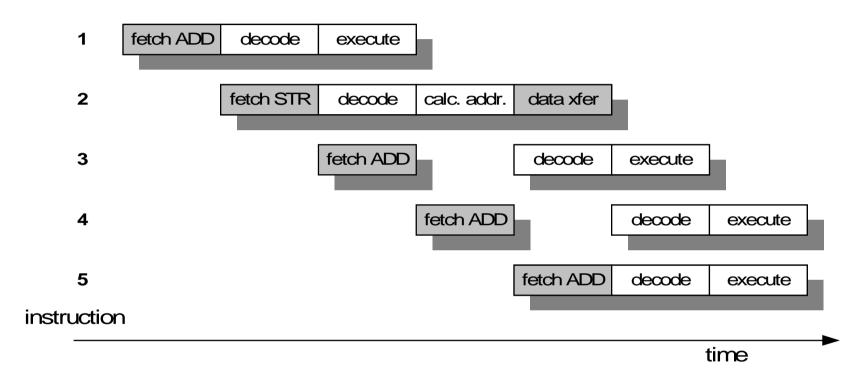

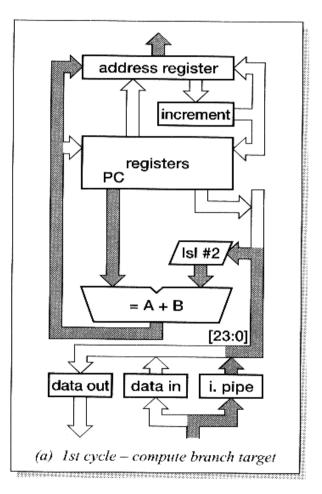

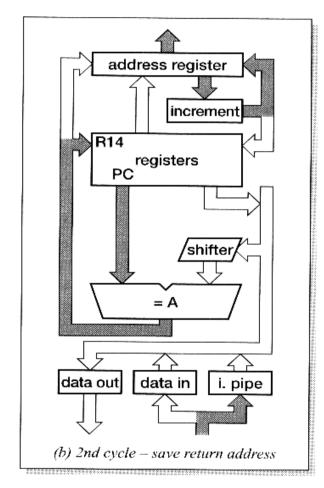

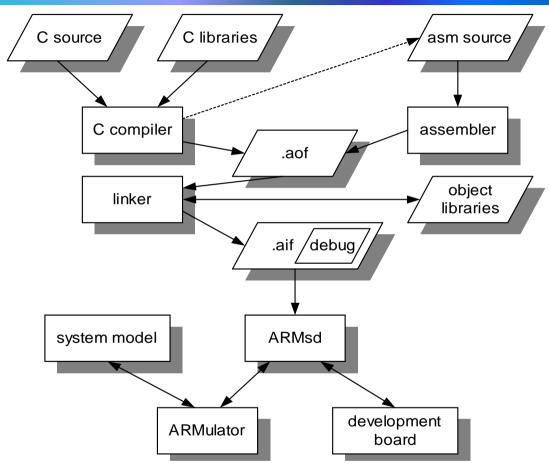

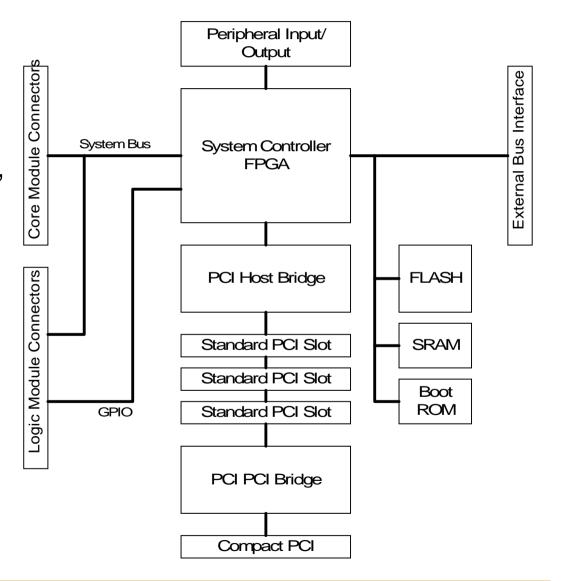

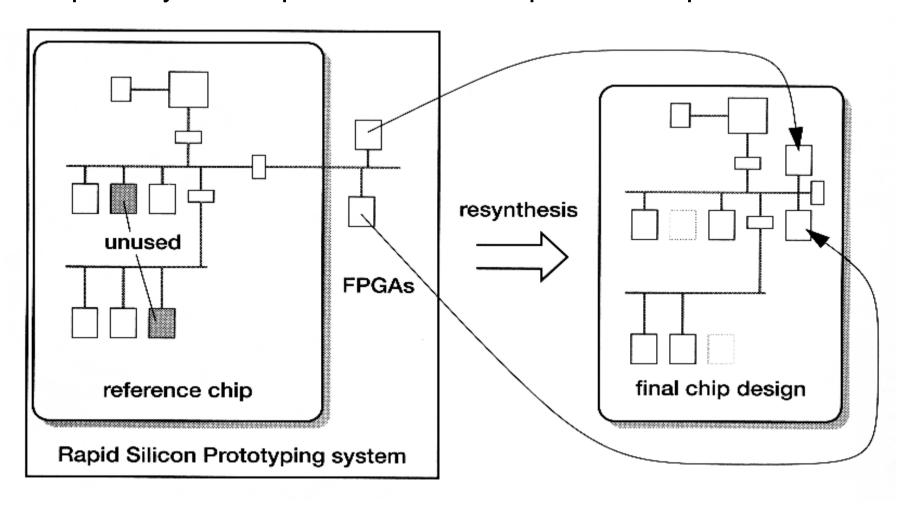

BX r5