## HW3

Exercise: 3.8, 3.9, 3.10, 3.11, 3.17, 3.19, 3.22, 3.23, 3.24, 3.30, 3.32, 3.33, 3.34

- **3.8** [5] <\$3.2> Assume 185 and 122 are signed 8-bit decimal integers stored in sign-magnitude format. Calculate 185 2 122. Is there overflow, underflow, or neither?

- **3.9** [10] <\$3.2> Assume 151 and 214 are signed 8-bit decimal integers stored in two's complement format. Calculate 151 + 214 using saturating arithmetic. The result should be written in decimal. Show your work.

- **3.10** [10] <\$3.2> Assume 151 and 214 are signed 8-bit decimal integers stored in two's complement format. Calculate 151 2 214 using saturating arithmetic. The result should be written in decimal. Show your work.

- **3.11** [10] <\$3.2> Assume 151 and 214 are unsigned 8-bit integers. Calculate 151 + 214 using saturating arithmetic. The result should be written in decimal. Show your work.

```

Fix 3.8

```

- X: Calculate 182 2 122.

- O: Calculate 182 122.

## Fix 3.10

- X: Calculate 151 2 214.

- O: Calculate 151 214.

- **3.17** [20] <\$3.3> As discussed in the text, one possible performance enhancement is to do a shift and add instead of an actual multiplication. Since  $9 \times 6$ , for example, can be written  $(2 \times 2 \times 2 + 1) \times 6$ , we can calculate  $9 \times 6$  by shifting 6 to the left 3 times and then adding 6 to that result. Show the best way to calculate  $0 \times 33 \times 0 \times 55$  using shifts and adds/subtracts. Assume both inputs are 8-bit unsigned integers.

## Fix 3.17

- X:  $0 \times 33 \times 0 \times 55$

- O:  $0x33 \times 0x55$  (hexadecimal)

**3.19** [30] <\$3.4> Using a table similar to that shown in Figure 3.10, calculate 74 divided by 21 using the hardware described in Figure 3.11. You should show the contents of each register on each step. Assume A and B are unsigned 6-bit integers. This algorithm requires a slightly different approach than that shown in Figure 3.9. You will want to think hard about this, do an experiment or two, or else go to the web to figure out how to make this work correctly. (Hint: one possible solution involves using the fact that Figure 3.11 implies the remainder register can be shifted either direction.)

| Iteration  | Step                                           | Quotient | Divisor   | Remaind   |

|------------|------------------------------------------------|----------|-----------|-----------|

| itteration |                                                | 0000     | 0010 0000 | 0000      |

| 0          | Initial values                                 | 0000     | 0010 0000 | 0000 011  |

| 1          | 1: Rem = Rem - Div                             | 0000     | 0010 0000 | ①110 011  |

|            | 2b: Rem $< 0 \Rightarrow +Div$ , sll Q, Q0 = 0 |          | 0001 0000 | 0000 01   |

|            | 3: Shift Div right                             | 0000     |           | 0000 01:  |

| 2          | 1: Rem = Rem - Div                             | 0000     | 0001 0000 | U111 01-  |

|            | 2b: Rem < 0 ⇒ +Div, sll Q, Q0 = 0              | 0000     | 0001 0000 | 0000 011  |

|            | 3: Shift Div right                             | 0000     | 0000 1000 | 0000 011  |

| 3          | 1: Rem = Rem - Div                             | 0000     | 0000 1000 | @111 111  |

|            | 2b: Rem < 0 ⇒ +Div, sll Q, Q0 = 0              | 0000     | 0000 1000 | 0000 011  |

|            | 3: Shift Div right                             | 0000     | 0000 0100 | 0000 011  |

| 4          | 1: Rem = Rem - Div                             | 0000     | 0000 0100 | ©000 001  |

|            | 2a: Rem ≥ 0 ⇒ sll Q, Q0 = 1                    | 0001     | 0000 0100 | 0000 001  |

|            | 3: Shift Div right                             | 0001     | 0000 0010 | 0000 001  |

| 5          | 1: Rem = Rem - Div                             | 0001     | 0000 0010 | ©000 000  |

|            | 2a: Rem ≥ 0 ⇒ sll Q, Q0 = 1                    | 0011     | 0000 0010 | 0000 0000 |

|            | 3: Shift Div right                             | 0011     | 0000 0001 | 0000 0000 |

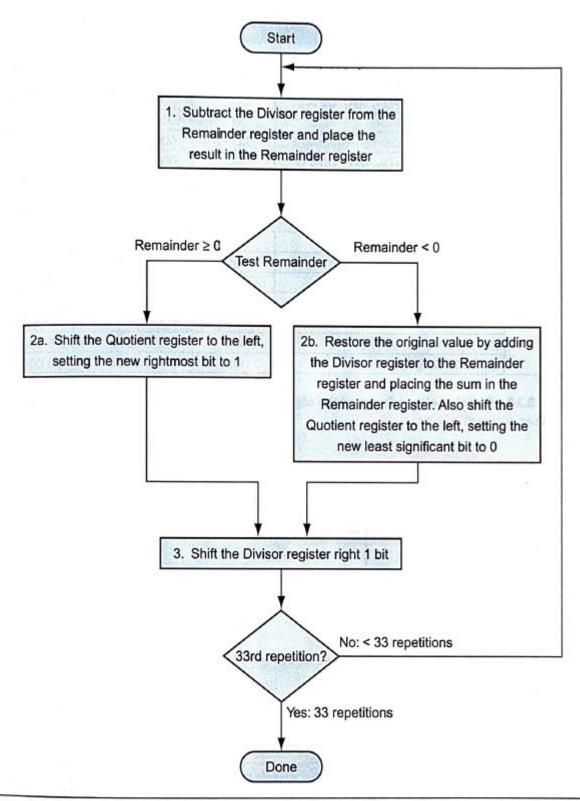

FIGURE 3.10 Division example using the algorithm in Figure 3.9. The bit examined to determine the next step is circled in color.

PIGURE 3.11 An improved version of the division hardware. The Divisor register, ALU, and Quotient register are all 32 bits wide, with only the Remainder register left at 64 bits. Compared to Figure 3.8, the ALU and Divisor registers are halved and the remainder is shifted left. This version also combines the Quotient register with the right half of the Remainder register. (As in Figure 3.6, the Remainder register should really be 65 bits to make sure the carry out of the adder is not lost.)

**FIGURE 3.9** A division algorithm, using the hardware in Figure 3.8. If the remainder is positive, the divisor did go into the dividend, so step 2a generates a 1 in the quotient. A negative remainder after step 1 means that the divisor did not go into the dividend, so step 2b generates a 0 in the quotient and adds the divisor to the remainder, thereby reversing the subtraction of step 1. The final shift, in step 3, aligns the divisor properly, relative to the dividend for the next iteration. These steps are repeated 33 times.

- **3.22** [10] <\$3.5> What decimal number does the bit pattern  $0 \times 0000000$  represent if it is a floating point number? Use the IEEE 754 standard.

- **3.23** [10] <\$3.5> Write down the binary representation of the decimal number 63.25 assuming the IEEE 754 single precision format.

- **3.24** [10] <\$3.5> Write down the binary representation of the decimal number 63.25 assuming the IEEE 754 double precision format.

- **3.30** [30] <\$3.5> Calculate the product of  $-8.0546875 \times 10^{\circ}$  and  $-1.79931640625 \times 10^{-1}$  by hand, assuming A and B are stored in the 16-bit half precision format described in Exercise 3.27. Assume 1 guard, 1 round bit, and 1 sticky bit, and round to the nearest even. Show all the steps; however, as is done in the example in the text, you can do the multiplication in human-readable format instead of using the techniques described in Exercises 3.12 through 3.14. Indicate if there is overflow or underflow. Write your answer in both the 16-bit floating point format described

in Exercise 3.27 and also as a decimal number. How accurate is your result? How does it compare to the number you get if you do the multiplication on a calculator?

- **3.32** [20] <\$3.9> Calculate (3.984375  $\times$  10<sup>-1</sup> + 3.4375  $\times$  10<sup>-1</sup>) + 1.771  $\times$  10<sup>3</sup> by hand, assuming each of the values are stored in the 16-bit half precision format described in Exercise 3.27 (and also described in the text). Assume 1 guard, 1 round bit, and 1 sticky bit, and round to the nearest even. Show all the steps, and write your answer in both the 16-bit floating point format and in decimal.

- **3.33** [20] <\$3.9> Calculate  $3.984375 \times 10^{-1} + (3.4375 \times 10^{-1} + 1.771 \times 10^{3})$  by hand, assuming each of the values are stored in the 16-bit half precision format described in Exercise 3.27 (and also described in the text). Assume 1 guard, 1 round bit, and 1 sticky bit, and round to the nearest even. Show all the steps, and write your answer in both the 16-bit floating point format and in decimal.

- **3.34** [10] <\$3.9> Based on your answers to 3.32 and 3.33, does (3.984375  $\times$  10<sup>-1</sup> + 3.4375  $\times$  10<sup>-1</sup>) + 1.771  $\times$  10<sup>3</sup> = 3.984375  $\times$  10<sup>-1</sup> + (3.4375  $\times$  10<sup>-1</sup> + 1.771  $\times$  10<sup>3</sup>)?

- **3.27** [20] <\$3.5> IEEE 754-2008 contains a half precision that is only 16 bits wide. The leftmost bit is still the sign bit, the exponent is 5 bits wide and has a bias of 15, and the mantissa is 10 bits long. A hidden 1 is assumed. Write down the bit pattern to represent  $-1.5625 \times 10^{-1}$  assuming a version of this format, which uses an excess-16 format to store the exponent. Comment on how the range and accuracy of this 16-bit floating point format compares to the single precision IEEE 754 standard.

- **3.12** [20] <\$3.3> Using a table similar to that shown in Figure 3.6, calculate the product of the octal unsigned 6-bit integers 62 and 12 using the hardware described in Figure 3.3. You should show the contents of each register on each step.

- **3.13** [20] <\$3.3> Using a table similar to that shown in Figure 3.6, calculate the product of the octal unsigned 8-bit integers 62 and 12 using the hardware described in Figure 3.5. You should show the contents of each register on each step.

- **3.14** [10] <\$3.3> Calculate the time necessary to perform a multiply using the approach given in Figures 3.3 and 3.5 if an integer is 8 bits wide and each step of the operation takes 4 time units. Assume that in step 1a an addition is always performed—either the multiplicand will be added, or a zero will be. Also assume that the registers have already been initialized (you are just counting how long it takes to do the multiplication loop itself). If this is being done in hardware, the shifts of the multiplicand and multiplier can be done simultaneously. If this is being done in software, they will have to be done one after the other. Solve for each case.

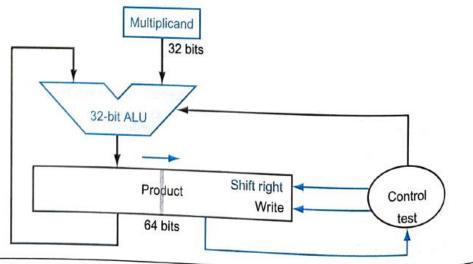

Figure 3.3. The Multiplicand register, ALU, and Multiplier register are all 32 bits wide, with only the Product register left at 64 bits. Now the product is shifted right. The separate Multiplier register also disappeared. The multiplier is placed instead in the right half of the Product register. These changes are highlighted in color to highlight the evolution from Figure 3.3.)

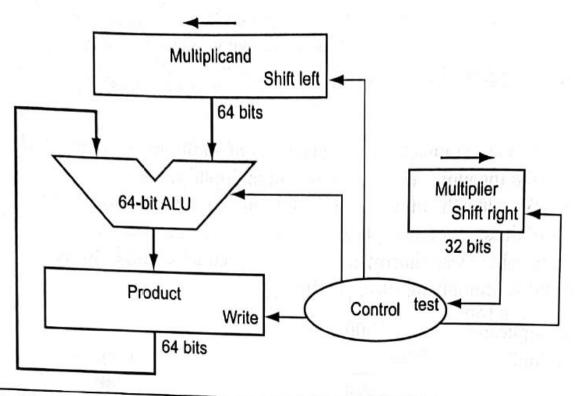

FIGURE 3.3 First version of the multiplication hardware. The Multiplicand register, ALU, and Product register are all 64 bits wide, with only the Multiplier register containing 32 bits. (Appendix B describes ALUs.) The 32-bit multiplicand starts in the right half of the Multiplicand register and is shifted left 1 bit on each step. The multiplier is shifted in the opposite direction at each step. The algorithm starts with the product initialized to 0. Control decides when to shift the Multiplicand and Multiplier registers and when to write new values into the Product register.

| Iteration | Step                                        | Multiplier | Multiplicand | Product   |

|-----------|---------------------------------------------|------------|--------------|-----------|

|           | Initial values                              | 001①       | 0000 0010    | 0000 0000 |

| 0         | Initial values  1a: 1 ⇒ Prod = Prod + Mcand | 0011       | 0000 0010    | 0000 0010 |

| 1         | 2: Shift left Multiplicand                  | 0011       | 0000 0100    | 0000 0010 |

|           | 3: Shift right Multiplier                   | 000①       | 0000 0100    | 0000 001  |

| 2         | 1a: 1 ⇒ Prod = Prod + Mcand                 | 0001       | 0000 0100    | 0000 011  |

|           | 2: Shift left Multiplicand                  | 0001       | 0000 1000    | 0000 011  |

|           | 3: Shift right Multiplier                   | 0000       | 0000 1000    | 0000 011  |

| 3         | 1: 0 ⇒ No operation                         | 0000       | 0000 1000    | 0000 011  |

|           | 2: Shift left Multiplicand                  | 0000       | 0001 0000    | 0000 0110 |

|           | 3: Shift right Multiplier                   | 0000       | 0001 0000    | 0000 0110 |

| 4         | 1: 0 ⇒ No operation                         | 0000       | 0001 0000    | 0000 0110 |

|           | 2: Shift left Multiplicand                  | 0000       | 0010 0000    | 0000 0110 |

|           | 3: Shift right Multiplier                   | 0000       | 0010 0000    | 0000 0110 |

FIGURE 3.5 Multiply example using algorithm in Figure 3.4. The bit examined to determine the next step is circled in color.